Center-Aligned PWM Output

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW FPGA Module

- LabVIEW Real-Time Module

- LabVIEW

Software

Code and Documents

Attachment

Overview

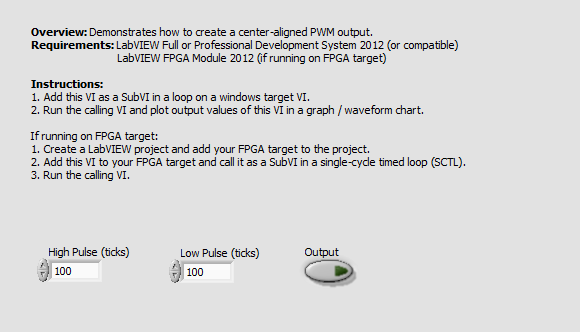

This example demonstrates how to create a center-aligned PWM output.

Description

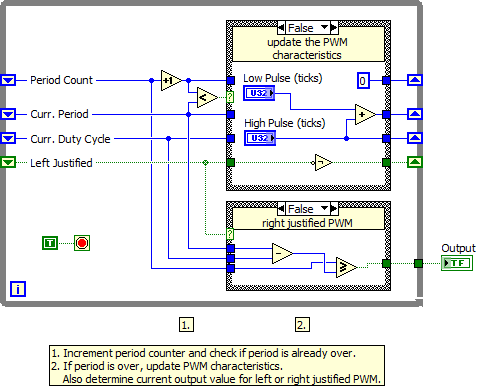

This block of code produces a center-aligned PWM output to be used in motion control applications. In a FET or IGBT bridge such as an H-bridge, use of a center-aligned PWM means that the switches change state half as frequently as they would when using a normal PWM signal. This reduces wear on the switches, decreases the heat generated by the FETs or IGBTs and also improves the dynamic characteristics of the system. The code has been designed to run in a single-cycle timed loop so that with a high-speed digital output on a cRIO or FPGA card, the PWM signal can update on the FPGA clock cycle. It can also be executed on windows and real-time targets.

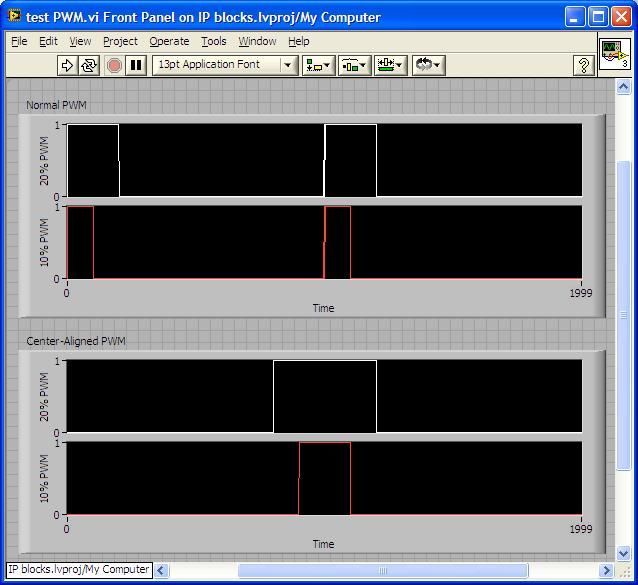

The image below shows two normal PWM signals on the top graph, the first with a 20% duty cycle and the second with a 10% duty cycle. The second graph shows the same PWM signals using the center-aligned PWM output.

Requirements

Software

- LabVIEW Full or Professional Development System 2012 (or compatible)

- If running in a Real-Time context, you will need the LabVIEW Real-Time Module 2012 (or compatible)

- If running in a FPGA context, you will need the LabVIEW FPGA Module 2012 (or compatible)

Hardware

- FPGA and Real-Time target optional (e.g. cRIO 9074 or compatible)

Steps to Implement or Execute Code

- Download and open the attached file "Center-Aligned PWM Generation LV2012 NIVerified.vi"

- Follow the instructions in Front Panel and Block Diagram and run the program

Additional Information or References

**The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text ‘NIVerified’. Read here for more information about the new Example Guidelines and Community Platform.**

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.