Biphase Manchester Encoding IP

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW

Software

Code and Documents

Attachment

Overview

This example generates data and transforms it into a biphase Manchester encoded signal. This VI also utilizes FPGA block memory to store the generated data in the encoded form.

Description

Manchester coding is used in situations where you want eliminate data-dependent DC components, and/or where you want self-clocking behavior. Self-clocking means that a Manchester-encoded signal can actually be interpreted correctly without a clock signal.

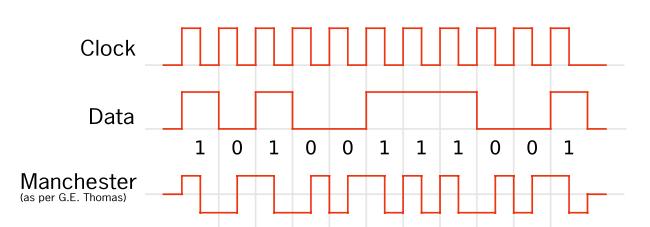

Manchester Encoding Functionality:

-- Each bit is transmitted in a fixed time (the "period").

-- A '0' is expressed by a low-to-high transition, a '1' by a high-to-low transition.

-- The transitions which signify 0 or 1 occur at the midpoint of the clock period.

-- Transitions at the start of a period are overhead and do not signify data. These are necessary when a series of 0's or 1's repeat.

Since we have a transition at least once for every data bit, we ensure that we won't have a DC signal if the data stays constant. Also, assuming data gets sent about the formation of the signal (or if both parties know the signal frequency), a clock signal is not necessary.

This diagram is an example of Manchester encoding:

Note that the data transfer always occurs at the falling clock edge. When the data repeats we have to do one of those "overhead" transitions on the rising clock edge.

Requirements

Software

LabVIEW 8.5 (or compatible)

LabVIEW FPGA

Hardware

(optional) NI FPGA with DIO capabilities

Steps to Implement or Execute Code

1) Download and extract attached zip file

2) Open project file.

3) Set the FPGA target to execute on the development computer, or add your own FPGA target to the project and move the VIs over

5) Open "FPGA Generate Manchester Signal Stream from Block Memory.vi" - if needed, modify the "Clock Out" and "Data Out" DIO lines to correspond with your new FPGA target

6) If needed, adjust the repetition rate and other signaling parameters

7) Run the VI

Additional Information or References

There is some additional IP included in this project

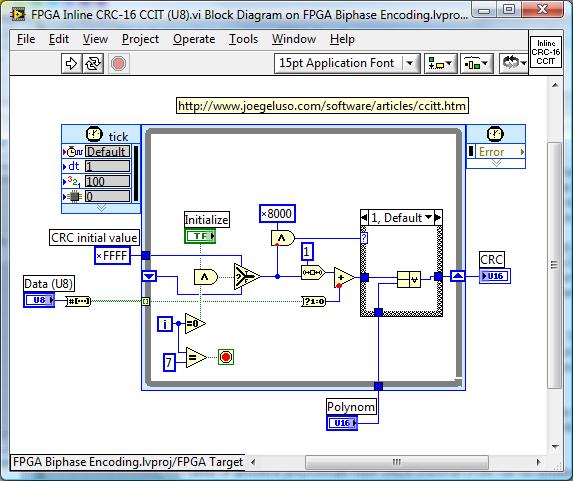

--an IP block for Inline 16-bit cyclic redundancy CCIT checking

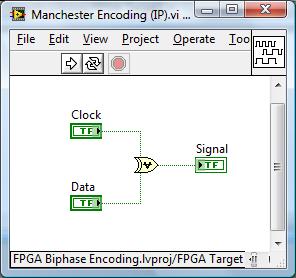

--An IP block that shows the logic behind Manchester encoding

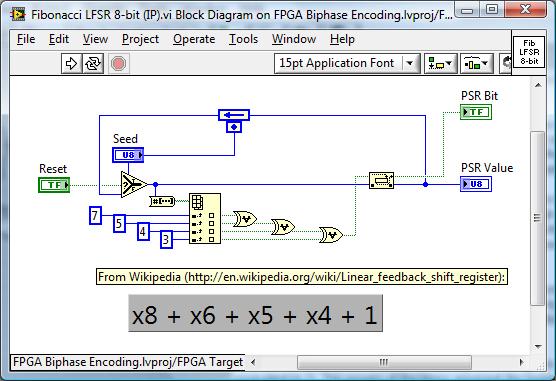

--An IP block for an 8-bit Fibonacci Linear Feedback Shift Register

**This document has been updated to meet the current required format for the NI Code Exchange.**

Installer R&D

National Instruments

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thanks help me a lot with the new FOBik - TRW Automotive

315.730.6012

mejemco@gmail.com