- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Introduction

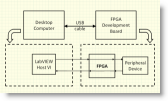

LabVIEW FPGA offers a completely new design flow for FPGA targets, and provides a unified and comprehensive environment for hands-on laboratory projects in digital circuits and systems. The graphical dataflow paradigm and LabVIEW programming environment offer many advantages over traditional HDL-based design flows, not only in terms of design entry, but for simulation, real-time debugging on the target, and host-to-FPGA communications.

“Digital Circuits and Systems with LabVIEW FPGA” presents a set of reference designs and techniques that show how LabVIEW FPGA covers the laboratory component of a standard first-semester introductory course in digital circuits and systems, from logic gate schematics to register transfer level (RTL) design. The reference designs illustrate basic and intermediate LabVIEW FPGA coding techniques and present example applications designed to motivate student interest in further study of digital systems. Narrated videos explain important concepts and show the LabVIEW FPGA tool in action. In addition, an IP library with examples provides immediate access to peripheral devices on the Spartan-3E Starter Kit board (rotary knob encoder, LCD, VGA, and switch debouncer) and the National Instruments Digital Electronics FPGA board (LED display and switch debouncer).

NOTE: The IP library linked below represents the official distribution; similar versions exist in the reference designs and work fine, but new designs should start with the IP linked below.

Table of Contents

| digsys-01: LabVIEW FPGA in the Digital Circuits and Systems Curriculum -- This article describes the motivation for using LabVIEW FPGA to support the hands-on activities of an introductory digital logic course as well as subsequent courses in digital systems, and details the advantages of LabVIEW FPGA compared to traditional laboratory CAD tools. |

| digsys-02: Bits, Buses, and Binary Numbers -- Binary signals serve as the foundation for every digital system. Working with discrete binary signals, grouping related signals into buses, extracting signals from buses, and interpreting groups of bits as binary numbers are prerequisite skills for creating combinational and sequential logic circuits with LabVIEW FPGA. This tutorial reviews techniques for working with the LabVIEW “Boolean” data type, Boolean arrays, and integer data type, and presents two LabVIEW application VIs to illustrate these techniques. |

| digsys-03: Implementation Styles for Combinational Circuits -- LabVIEW FPGA offers a wide range of styles to express a combinational circuit. This tutorial presents seven ways to implement a given circuit, including familiar traditional techniques found in digital logic textbooks as well as techniques likely to occur to experienced LabVIEW programmers. This tutorial also presents a complete audio meter application in which a host VI plays a .wav audio file on the sound card while simultaneously transferring real-time audio level values to the FPGA development board that are decoded by the FPGA to drive a linear LED array as a bar graph style audio meter. |

| digsys-04: Sequential Circuits at the Flip-Flop Level -- LabVIEW FPGA provides complete support for sequential logic circuits at the discrete flip-flop level as well as the register level. This article presents the LabVIEW while-loop combined with a shift register and equivalent feedback node as direct implementation of a D-type flip-flop, and then illustrates how common sequential circuits such as data registers, shift registers, sequence generators, and counters can all be easily implemented within LabVIEW FPGA. |

| digsys-05: Rapid Development of Device Interfaces with a Transparent FPGA -- Developing and debugging a peripheral interface on the FPGA target requires much time because each modification of the VI necessitates a complete rebuild of the FPGA bitstream file, no matter how minor the change. Even for very small designs, waiting two or three minutes to try the modified VI quickly becomes tiresome. Fortunately, the core functionality of many VIs intended for the FPGA target runs quite well on the desktop. Placing the FPGA target in “transparent mode” effectively connects the desktop VI directly to the peripheral device of interest, and iterating the design on the host eliminates the need to rebuild the FPGA target. This article explains how to develop a peripheral interface with a transparent FPGA, and illustrates the technique with an example design process of a two-digit seven-segment display driver for the NI Digital Electronics FPGA board. |

| digsys-06: State Machines for FPGA-Based Controllers -- State machines, also known as finite state machines, play a vital role as controllers for digital systems. State machines belong to the sequential circuit family, and therefore contain a memory element to store the machine state as well as combinational logic to determine the state progression and output values. This article briefly reviews state machine hardware and state diagrams, describes how to implement and verify state machines in LabVIEW, and presents a practical example of a digital system controlled by a state machine implemented with LabVIEW FPGA – a garage door opener that includes a safety mechanism for obstructions. |

| digsys-07: RTL Design for Data-Oriented Systems -- LabVIEW offers full support for the traditional RTL (register transfer level) design methodology, and adds the benefit of its inherently graphical coding style. The VI block diagram preserves the visual nature of the RTL system diagram. This article reviews the RTL design process with associated terminology and notation, presents basic RTL constructs and simple examples, and steps through the design of a full-scale application example involving a VGA video display. |

| digsys-08: Design Case Study: Reaction Timer Electronics for a Children’s Museum Exhibit -- The capstone project in an introductory digital circuits and systems course provides students with an opportunity to apply register transfer level (RTL) and controller/datapath partition design techniques to solve a practical and interesting problem. This article presents a design project case study of the electronics module for a children’s museum “reaction timer” exhibit. |

| Switch Debouncer -- Mechanical switch bounce (or chatter) causes a single press of a button to yield many signal transitions in the sub-millisecond range. Debounce Switch.vi suppresses switch chatter for pushbuttons and slide switches to yield a clean signal. |

| LED Display Controllers -- Show Hex on LED Display.vi displays an unsigned 8-bit integer (U8 datatype) in hexadecimal format on the two-digit seven-segment LED display on the NI Digital Electronics FPGA board; Manage LED Display.vi provides direct control over the individual LED segments. |

| Rotary Knob Position -- Detects rotation of the rotary knob encoder used on the Spartan-3E Starter Kit FPGA development board (Digilent S3EBOARD) and reports its position relative to a “home” position. |

| LCD Device Driver -- This collection of subVIs provides support for the LCD on the Spartan-3E Starter Kit FPGA development board. The high-level subVIs Show Hex on LCD.vi and Show Character on LCD.vi display user-defined numerical values in hexadecimal format and as ASCII characters; lower-level subVIs provide access to the LCD controller command set, and serve as the foundation for other yet-to-be-created “Show” subVIs. Multiple instances of the “Show” subVIs may be used in a single application VI, with each controlling its own region of the LCD. |

| VGA Device Driver -- Manage VGA.vi drives the VGA port signal lines to create a 640x480 3-bit video image. The subVI provides the coordinates of the current pixel which the user-supplied circuit translates into the desired RGB color combination. |

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

this is an amazing series, I hope to find more of them (maybe one about accessing block memory (like a table) on an FPGA 😉

Certified LabVIEW Architect

cell: 516.819.9711

http://www.aleconsultants.com

larry@aleconsultants.com