- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

does diagram disable structure prevent compiling controls?

Solved!04-26-2024 12:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

im using crio with labview 2019 and have a question about diagram disable structure.

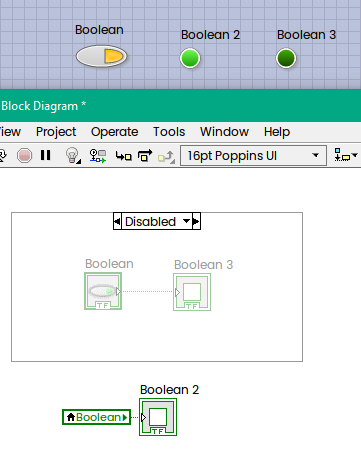

When i use it my disabled code are dimmed in the block diagram.

But on the control panel my controls are still vissible as usual.

So i wonder if my disabled controls are compiled anyway on my fpga and take up resourses,

even though they are inside a disabled structure?

Solved! Go to Solution.

04-29-2024 01:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This is how Diagram Disable works:

The code inside this structure is not compiled, but control still here, you can use, for example, local variables and they will work for you, some code to handle control still present, but not the code inside this structure.

04-29-2024 02:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In FPGA, a control is basically a register. Unless it is a string or array with huge default data, the used resources for that are extremely small and you are not likely to see any difference in resource usage with or without that control in your VI.

04-29-2024 02:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi tokar,

@tokar wrote:

When i use it my disabled code are dimmed in the block diagram.

But on the control panel my controls are still vissible as usual.

You disable "code that handles data flow" inside your block diagram.

You don't disable any frontpanel elements, they still exist...

04-29-2024 03:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Pretty sure I've seen host interfaces to FPGA controls disappear when they don't have an enabled reference (terminal\local?) on the diagram. This might have been a while ago, probably ~LV8.

I remember because I found it quite annoying. My API didn't work anymore as the control was removed... I wasn't concerned about speed and gates.

It look to me like the terminal actually causes the interface to host to be created, not the control. So if the terminal was disabled, I didn't get the interface to the host.

04-29-2024 04:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

A lot of good input in the threat now.

Thank you all for commenting.

Just to be clear i assuming your answer says that frontpanel elements in fact are taking up resources,

even though they are inside Diagram disable structure?

In an answer above i saw someone having a local variable pointing towards a boolean inside

a disable structure. That shouldnt be possible if the boolean itself arent there, so it must be present i guess and taking up resources on the FPGA.

04-29-2024 06:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@tokar wrote:Just to be clear i assuming your answer says that frontpanel elements in fact are taking up resources, even though they are inside Diagram disable structure?

I didn't, others did.

Why don't you try?

Make a VI with a control, check it's available on the host. Put the terminal in a disabled case, see if it's still available. Should be a 20 min. experiment and the only way to know for sure.

We all do agree it's nothing to worry about.

Unless you have hundreds of controls (in disabled cases), but even then: optimize (only) when needed.

If you have a resource shortage, post some code. I doubt it's the FP controls....

04-30-2024 02:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I did the compilation and actually i can reach the disabled fpga controls on my RT system with Read/write control.

So they are taking up resources.

Im using an old fpga and the compilation results varies. I also have alot of disabled optional code and i use approximately 99,6% of my slices so it actually counts. Many thanks for your tips. Case closed :).