- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI VeriStand FPGA-Based I/O Interface Tools Discussion

05-29-2016 11:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

Since English is not my native language, if there is anything unclear about my post above, please let me know and I'll be happy to describe it in another way. I realize it is Memorial day in the U.S., so I expect we won't be seeing any reply for the next few days. I'm looking forward to hear from any one of you after coming back from the break.

Regards,

Michi

06-23-2016 07:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Please let me know if I should add more information to describe the questions above.

Thank you in advance.

Michi

07-01-2016 10:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you select the MXIe-RIO Chassis on Real-Time Industrial Controller as the project type and select Create new System in the next step, you get this error when you click Next:

At this point the wizard is essentially dead; you cannot go Back or Next, or even open the Help. Only the Cancel button responds.

You can however use a Real-Time PXI instead and complete the procedure, then, modify the project to show the industrial controller instead of the PXI. I saw this in LabVIEW 2015 and 2015 SP1.

National Instruments

11-02-2016 05:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Stephen,

I am using PXI-7811R(Connector0 0-39DO;Connector1 0-39DO;Connector2 0-9PWMOut,10-14DO;Connector3 0-22DI,23-39DO). I created a fpga personality and added to a VeriStand project. Everything went smoothly until I tried to deploy it. I am getting the following error.

The VeriStand Gateway encountered an error while deploying the System Definition file.

Details:

Error -50400 occurred at Project Window.lvlib:Project Window.vi >> Project Window.lvlib:Command Loop.vi >> Project Window.lvlib:Connect to System.vi

Possible reason(s):

The transfer operation was not completed within the timeout period or the specified number of retries。

=========================

NI VeriStand: HP Loop.lvlib:HP Loop Main.vi<APPEND>

Complete call chain:

HP Loop.lvlib:HP Loop Main.vi

NI VeriStand Engine.lvlib:VeriStand Engine State Machine.vi

NI VeriStand Engine.lvlib:VeriStand Engine.vi

NI VeriStand Engine.lvlib:VeriStand Engine Wrapper (RT).vi

Annex is the relate project.Any suggestion is appriciated.

Best regards.

Ning.

12-15-2017 11:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

How can I use these tools for the analog in and out of a NI-9381?

01-11-2018 12:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi All - I'm trying to modify existing FPGA code created in LabVIEW 2013 that is used for a Veristand Project. I am attempting to use LabVIEW 2016 and Veristand 2016. I'm having the following problems:

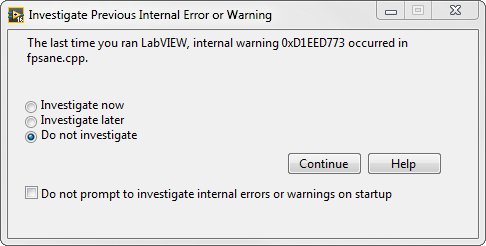

1. Ever since I installed "NI VeriStand FPGA Interface Tools 2010+ 1.3.0.zip", when I start LabVIEW 2016 to look at the code, I see the following. Maybe this is a side topic.

2. When I open the main vi after opening the project and LabVIEW searches for dependancies, I always have to direct it to C:\Program Files (x86)\National Instruments\VeriStand 2016\nivs.lib\Reference Assemblies to find NationalInstruments.Veristand.systemStorageUI.dll.

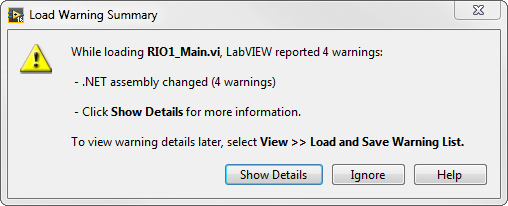

3. When the vi opens, I get the following warning. See warnings.txt in the attached zipfile.

Note that I see the same warning if I attempt to place an instance of "Veristand FPGA XML Builder" vi into the block diagram.

4. When I build the fpgaconfig and bitfile and attempt to attach it to an empty test Veristand project system definition file at Untitled7->Targets->Controller->Hardware->Chassis->FPGA->Add FPGA Target, I get the following warnings. See more details in attached files warnings2.txt and warnings3.txt.

5. When I press continue, System Explorer returns to the main screen without having added the FPGA configuration.

Thanks for any help that you can provide!

01-11-2018 12:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For problem #4 below, seems I forgot to copy the .xsd file per instructions "4. Copy the bitfile, config file, and schema (.xsd) in to either your NI VeriStand project directory or into the globally available Public Documents\National Instruments\<NI VeriStand Version>\FPGA directory." from the instruction sheet.

04-12-2018 03:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello all,

I'm trying to use an FPGA personality on a cRIO-9066. I have created the FPGA personality along with the xml file (using the XML file add-on), updated the Versitand project and tried to deploy.

I am getting an error -307660 (timeout error) when deploying. There's not much detail on this error so I am wondering if anyone might have tips on the cause?

The FPGA bitfile and XML file are copied to the "Public Documents\National Instruments\Veristand 2015\FPGA" folder (no .xsd file as I don't know where/how this is created).

Regards,

Dave

07-23-2018 11:07 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You are exactly right, this problem has puzzle me a lot of time

11-27-2019 01:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

How best to fix up template-generated VIs for a PXIe-7857R?

If I build the VS FPGA Template for 7853R I get the PXI Timing VIs on the diagram of the top-level FPGA VI.

If I build the VS FPGA Template for 7857R I get the cRIO Timing VIs on the diagram of the FPGA VI.

The template for 7853R gets me closer, so I build it and then add a FPGA Target 7857R in the LabVIEW project.

But when I drag the FPGA VI from the 7853R target to the 7857R target, many of the template subvis break because the I/O nodes are for the 7853R. I'm going to just replace those nodes with nodes that work on the 7857R.

Is that a good plan? Is there some other approach to this? Will this tool be updated for newer FPGA cards? Does anyone even use FPGA IO with Veristand? Thanks. cc