- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VeriStand FPGA XML Builder Node Feedback

10-21-2014 06:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for all the help guys!! I have attached my FPGA VI.

10-21-2014 06:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for attaching the VI, I'll look into why the extra category was thrown in there.

I also noticed that all of your scale values are 0. This means that of your values to and from the FPGA will also be 0. We are planning on making future revisions of the node use a default of 1 for PWM or FXP signals but you'd still need to input a proper scale for all other types. You'll want to modify the scale inputs and regenerate your XML so that you'll be able to send/receive correct values.

--Ryan_S

10-21-2014 06:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for letting me know about the scale. I will update it and regenerate the XML.

10-23-2014 10:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

is a Veristand FPGA XML Builder Node for LabView 2014 planned?

Thanks, Arnold

10-23-2014 12:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Hissi,

Yes, LabVIEW 2014 support was added to the node, I just hadn't uploaded it so thank you for asking. The latest version of the node (ver. 1.1.0) can be found on its add-ons page along with the necessary .NET configuration file for installing with LabVIEW 2014. Happy developing!

--Ryan_S.

10-28-2014 08:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

It seems that with the last version the default scale value has been set too for the int (I8, U8, ..). For this type of data, 1 isn't the good value.

From the VS help :

Scale : Specifies the range of the scale in engineering units. For PWM and fixed-point data types, the default value is 1. For all other data types, the default value is the full positive range of the data type. For example, the full positive range of the signed 8-bit data type is 127, and the full positive range of the unsigned 8-bit data type is 255.

The display on the Workspace was not correct for our int data. We have suppress the scale and offset in the fpgaconfig file and now it is working correctly.

Regards

Hubert

10-28-2014 08:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

Any way we could have access to the code generated by this express VI ?

Cheers

Mathieu

10-28-2014 08:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Mathieu,

Take an image of the block diagram within the XNode and store it at "<LabVIEW Data>\ VeriStand FPGA XML Script VI Block Diagram.png" which you can use to validate the block diagram. But currently there isn't an easy way to get access to the code itself.

I think its possible to do this and it wouldn't be too much of a code addition. Is the primary reason so that you could easily modify something or just to validate the design?

10-28-2014 10:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Hubert,

You are correct, within the node, the current default value for scale for all data types is 1 (previous versions it was 0). While this does not yet comply with the VeriStand help, we are working in that direction. Until then, you will need to enter a proper scale for each integer datatype (same as in previous versions) but no longer need to enter a scale for PWM, DIO, or FXP datatypes. Its important to note that in many cases, the scale for an integer channel won't be the full range of the datatype if you want scaled voltage to be returned.

Mathieu,

As Tim mentioned, the node does take a picture of the scripted code and store it in the LabVIEW Data directory to be used for debugging. This is also discussed in the "Instructions for Use" pdf. We would be interested in your feedback and specific need for the scripted code.

--Ryan_S.

10-29-2014 05:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ryan, Timothy,

Thanks for pointing out the "Instruction for use" again. Didn't read it carefully enough

In my case, it's enough for me to check the code.

- It would helpfull in the code screenshot, to be able to check the FXP format (e.g. display the FXP format in the label of the constant of the integer to fixed-point cast node)

- It would be interesting to have an option to have the generated code use (or not) the feedback node (that are used to reduce jitter)

- It would be event better to have a snapshot of the code, so that we could re-import the snapshot into LV to use and modify the generated code

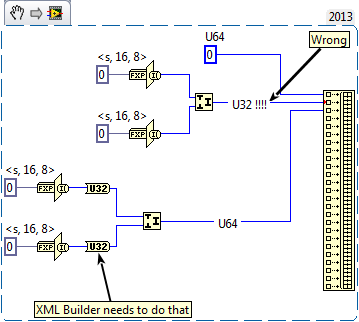

On top of that, when using (signed) FXP 16 bits in the FPGA, the FPGA XML builder doens't group them by 4 per packet. It groups them by 2 per packet only (most probably due to the fact that VS doesn't handle FXP16).

In the meanwhile, the fixed-point to integer cast node output format is I16, which mean that 2xFXP16 are cast to 2xI16, then grouped to a 32 bits word that is directly wired to the build array node (whose format is U64)

I guess there is no way to force the FPGA XML Builder to do this

Thanks for reading me.

Cheers