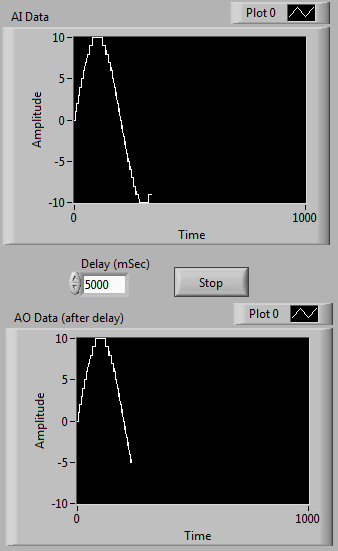

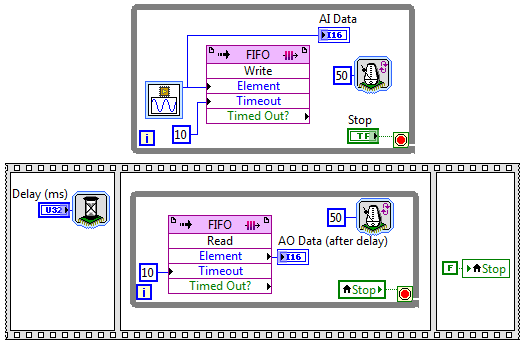

This is an example I threw together for a customer that I thought would be helpful to put out there. It is currently set up to delay a generated sine waveform, but that along with the indicators could be replaced with I/O nodes, and the timing functions in the loops are just for demonstration visibility. There are also delay functions in the FPGA Math & Analysis palette which perform the same functionality using arrays, but the delay input is limited to 8 bits which doesn't allow for long delays (due to the subsequent array size that would be needed).