How to Decrease the Update Delay with Analog Output in a cDAQ 9188

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Code and Documents

Attachment

Introduction

Because the cDAQ 9188 and 9181 communicates via Ethernet, a buffer is required to handle network events. This means that with analog output with non-regeneration, you can write a lot of data faster than you can output this data from the chassis. This can cause a delay between the time the user changes the frequency or amplitude of the output signal and the time the device under test receives the updated signal (because the time the data is written occurs before it is actually output).

Steps to Complete

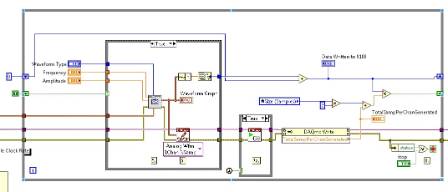

To decrease this delay, you need to keep track of how much data has been written and how much has actually been generated and slow down the DAQmx write. This example makes sure that the the DAQmx Write function is only 2 buffer sizes ahead of the actual generation, so when the frequency or amplitude is changed by the user, these values will be generated within the 2 buffer sizes.

Additional Notes

The buffer size and sampling rate with this VI determine the delay. If the buffer size is 5000 samples and the sampling rate is 5000 S/s, then the delay would be 2 seconds (because the write function is 2 buffer sizes ahead of the generation). If you are sampling at a faster rate, the number of buffer sizes that the write function is ahead of the generation may need to be increased.

NOTE: If there is a network hiccup, a buffer underflow condition could occur using this method. You may need to use error handling to clear and restart tasks if such an event occurs.

National Instruments

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Very useful VI - thanks. I have found that the same issue applies when using the cDAQ-9191 wireless chassis for analog output (with 9263 module). I found this VI solved the problem.