FPGA Serializer/Deserializer

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Code and Documents

Attachment

Overview

These VIs are meant to help with development of a digital protocol in FPGA. The serializer is useful for the transmit side where an integer input is serialized into bits until ready for the next word. The deserializer works in the receive code by taking input bits and creating an integer output. Both VIs are polymorphic, supported in SCTLs, and support up to 64-bit integers.

Everything was ported to LabVIEW 2009, but comment below is something appears broken.

Serializer

| Input | Description |

|---|---|

Parallel Word | The integer to be serialized |

| Output Bit? | A handshaking signal to control the ability to output the next bit of the word |

| New Word? | A handshaking signal to signify whether Parallel Word is a new integer. |

| Output | Description |

|---|---|

| Serial Data | The next bit of the word for output |

| Serial Index | A status indicator to show the current bit being output |

| Valid Bit | A handshaking signal to signal downstream logic that the current output bit is valid |

| Ready for New Word | A handshaking signal to signal upstream logic to supply a new integer word |

Deserializer

| Input | Description |

|---|---|

| Serial Input | The input bit to be parallelized |

| Input Valid | A handshaking signal to indicate that the Serial Input is a valid bit. |

| Output | Description |

|---|---|

| Parallel Output | The integer word resulting from the input serial data |

| Parallel Index | A status signal indicating the current input bits location in the integer (from MSB). |

| Output Valid | A handshaking signal indicating the Parallel output is a valid integer |

Usage

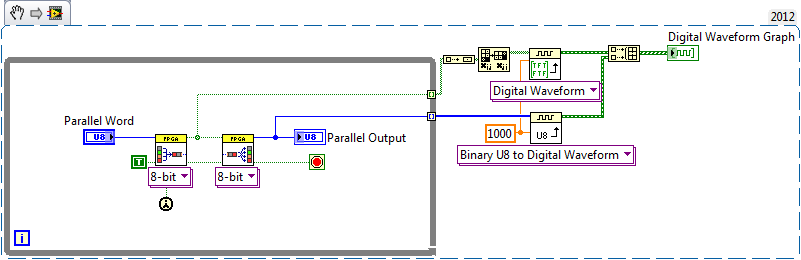

Attached is an example VI (SerializerDeserializerTest.vi) taking the input word, serializing the data, and deserializing the word. The serialization/deserialization is displayed on a digital waveform graph. The handshaking signals would be helpful for streaming applications, where a high throughput must be attained.

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thank you for your VI(s). Is the SerializerDeserializerTest.vi intended to be used as a Host VI? I ask because some of the functions used by SerializerDeserializerTest.vi are not supported by FPGA targets

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

The serializer/deserializer were meant to be run on FPGA. The Test VI just runs them in a Windows context as a simulation, to use as a full FPGA application would require moving the Serializer/Deserializer to FPGA and DMA FIFOs to transfer data as needed.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thank you for your response.

Should I read the Digital Waveform Graph as red/ Line 1 = LSB or b0, pink/ Line 8 = MSB or

b7?

I have attached the graph for x10 and see binary 0001 0000 (b7..b0), reading from bottom to top on right column.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Line 8 would be the MSB. x10 for 8 lines look like "b00010000"

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thank you for the clarification.