- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

I2C Example for the NI PXIe-5644R

|

I2C Example for the NI PXIe-5644R »

This example implements inter-integrated circuit (I2C) communication through the DIO port on the NI PXIe-5644R, including support for both master and slave functionality. |

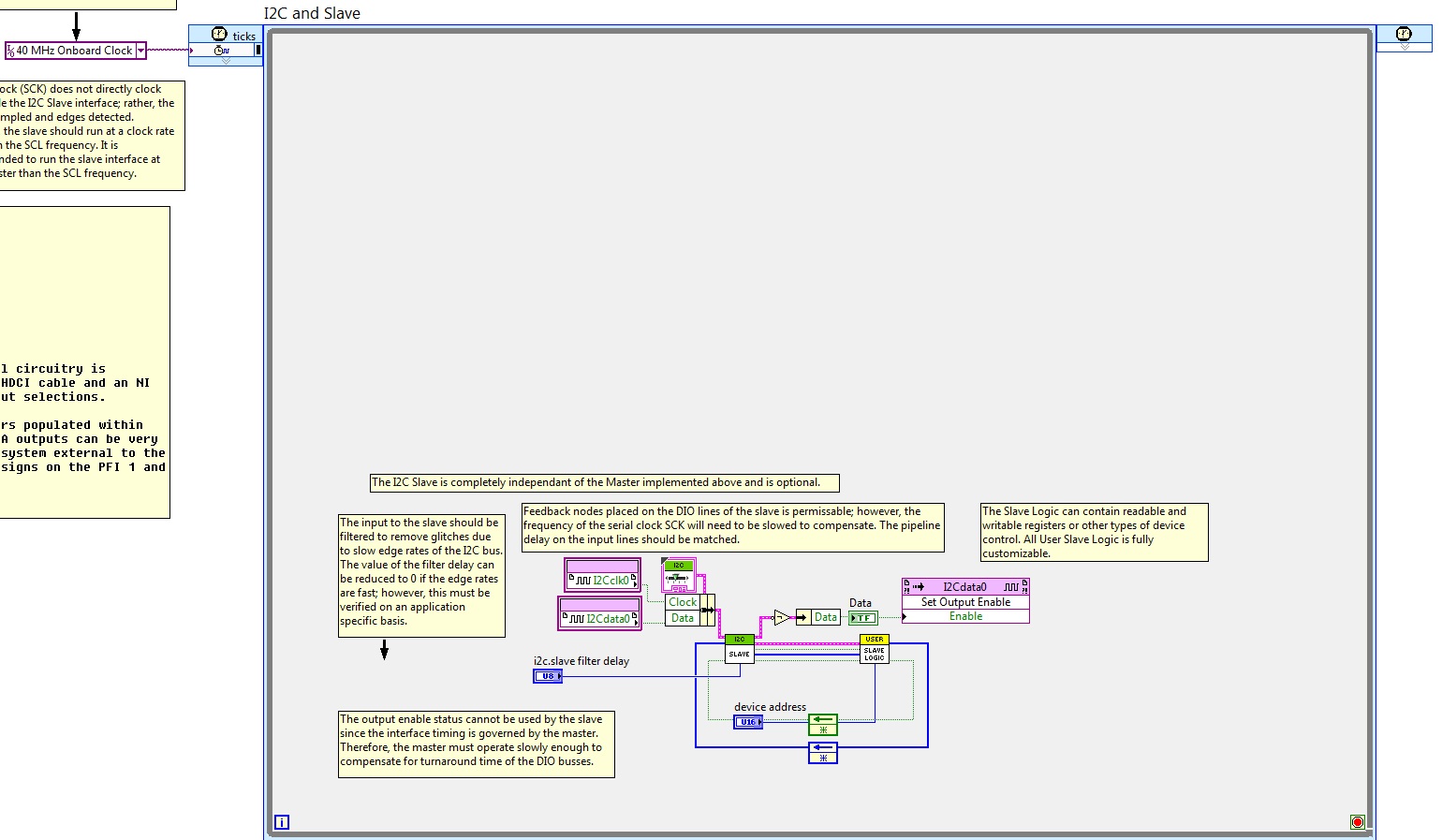

Description: Inter-Integrated Circuit (I2C) buses are commonly used to communicate between a controller (master) device and a target (slave) device. I2C buses require two lines for communication: clock (SCL) and serial data (SDA). This example contains LabVIEW FPGA code for both an I2C master and an I2C slave.

Additional Documentation:

- After Installation - C:\Program Files (x86)\National Instruments\LabVIEW 2012\examples\NI I2C Example for the NI PXIe-5644R\Documentation\NI 5644R Inter-Integrated Circuit (I2C) Example.pdf

Compatibility:

- LabVIEW Version: 2012

- Hardware: NI PXIe-5644R

Dependencies:

- NI LabVIEW 2012 Support for NI PXIe-5644R 1.0 (NI MSI installer)

- I2C IP (automatically resolved through VI package)

FPGA Footprint:

Xilinx Virtex-6 LX195T

- 4.9% / 6172 LUTs

- 3.2% / 7981 Flip-Flops

- 1.2% / 4 Block RAMs

- 0.0% / 0 DSP Slices

- ~100% compile success rate

Latest Version:

Previous Versions:

- none available

Note: All source on this community is distributed using VI Package Manager (VIPM). For more details on VIPM, please read A Note on VI Package Manager

Product Marketing Engineer

Signal Generators

National Instruments

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello Ryan,

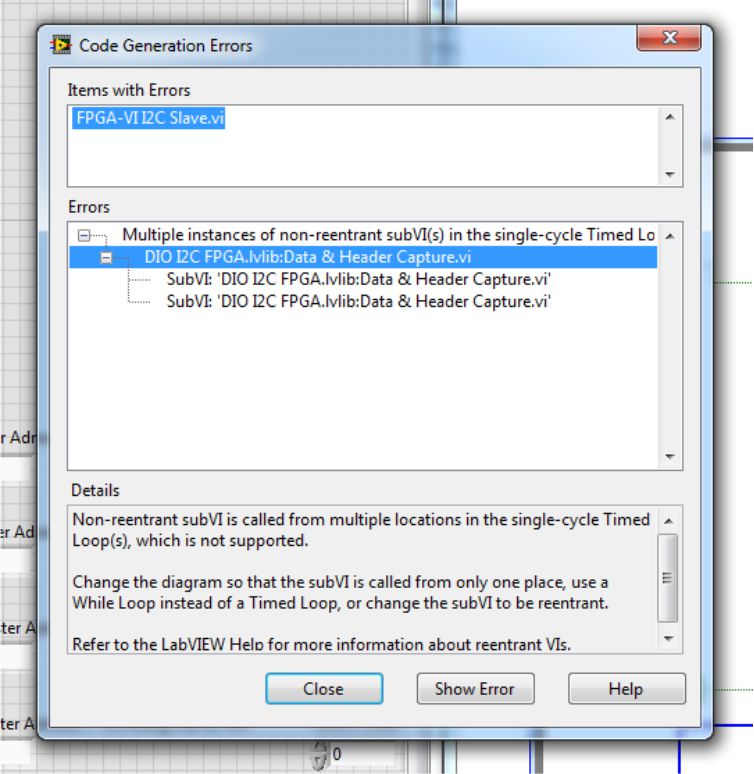

I try to build a FPGA-Configuration with two separated slaves. For this case I am using the I2C-Slave.vi from the "NI I2C Example for the NI PXIe 5644r". With one slave it works very good, but when I import a second slave, I get the following error;

Can you help me to solve this problem please? What I need is a simple copy of the I2C Slave.vi.

Thank you and best regards

Viktor

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi Viktor,

Looks like this VI should actually be marked as re-entrant. You should just modify the original VI on disk by going to VI properties -> execution settings, and changing the re-entrancy. You'll have to do this again if you re-install the package, but we'll add it to the list of updates for the next time we re-build this package. Thanks for the heads-up!

Regards,

Ryan

Product Marketing Engineer

Signal Generators

National Instruments

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi Ryan,

now it works. I have got to change the re-entrancy in the sub.vis data & header capture.vi and the pharse header.vi.

Thank you for the quick answer.

Regards

Viktor

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello,

Hello,

I have tried to make the I2C slave portion of this example, for the sbRIO. It seems to work for writing, but for reading, a logic analyzer shows that this I2C device always leaves the SDA line pulled low, after responding with a single byte.

The error I get on the I2C master (a NI USB-8451) is: "Error -301744 occurred at NI-845x I2C Write Read.vi:1 Possible reason(s): NI-845x: The I2C master lost arbitration and failed to seize the bus during transmission of an address+direction byte."

Note that the sbRIO does not have the ability to have output data and output enable in the same node. I have tried to have the method node before, and after the I/O node. Having just the output enable method works for writing, which is what is pictured.

Perhaps only the FlexRIO can work with this vi architecture ?

Thanks in advance for any thoughts on this.

Best,

Davy Baker