- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI and JSOL/JMAG Announce New Tools for ~1 MHz FEA-based Real-Time FPGA Simulation of PMSM Motor/Generator, Inverter & Load

06-04-2012 03:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

NEWS RELEASE – May 29, 2012 – National Instruments today introduced the JMAG-RT add-on for NI VeriStand, which gives engineers the same fidelity provided by proven JMAG models, but in real-time for hardware-in-the-loop (HIL) testing of electric motors.

- Xilinx FPGA-based real-time simulation delivers high-fidelity dynamic modeling based on FEA models with approximately 1 microsecond step times for unparalleled speed and accuracy.

- JMAG finite element analysis (FEA) electric motor models from JSOL integrate with NI VeriStand and NI reconfigurable I/O (RIO) hardware.

- NI’s complete HIL systems can be configured for most real-time motor or ECU test scenarios.

See the news release:

NI and JSOL Help Electric Motor Engineers Save Time, Money With HIL Modeling

Read a white paper for more in depth information:

High-Performance Electric Motor Simulation Using NI VeriStand and JMAG-RT

View a presentation on the new technology for integrating high-fidelity finite element analysis (FEA) in FPGA-based electric motor simulation using the JMAG-RT toolchain with NI VeriStand.

Presentation: High-Fidelity Electric Motor Simulation With NI VeriStand and JMAG-RT

A Look Under the Hood

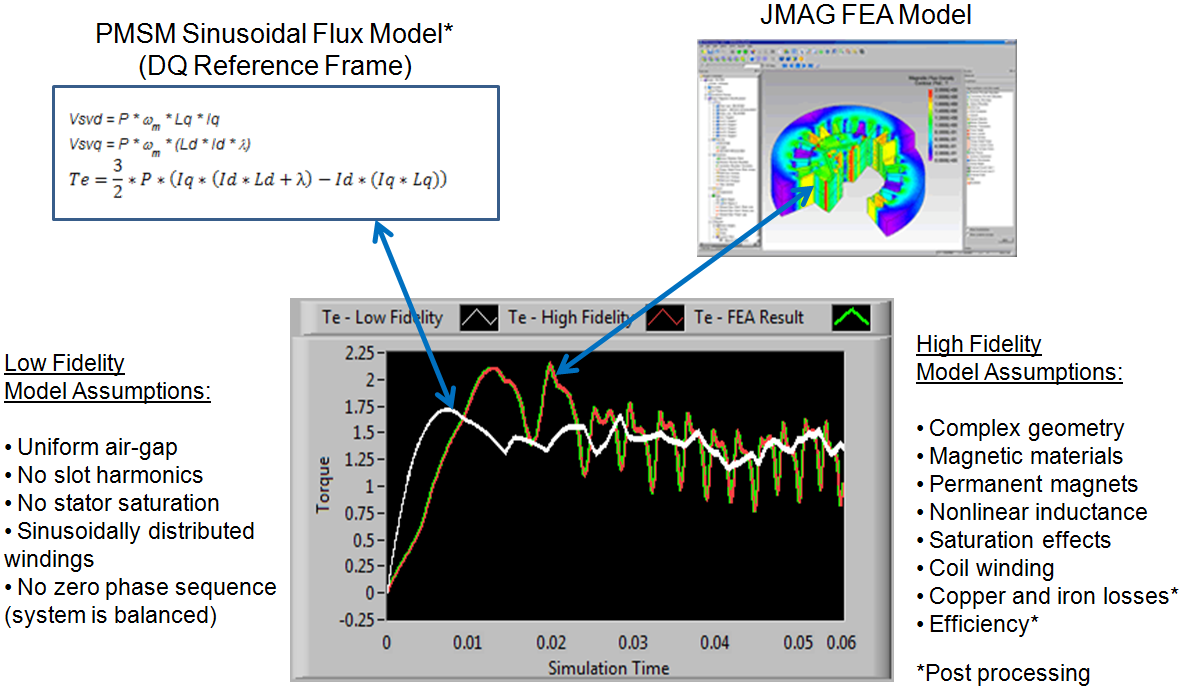

See below to get a feel for the accuracy of this new high fidelity, roughly 1 MHz JMAG-RT based simulation (running in LabVIEW FPGA on an NI FlexRIO board with 50 MS/s KGC analog front end (12 AI, 12 AO, 16 DI, 16 DO)) compared to traditional sinusoidal flux PMSM motor model. You can see how much more accurate the results are compared to the classic sinusoidal flux motor model that most people use for HIL simulation.

As you can see, there is a lot of complexity hidden in the non-linear magnetics of the machine that is captured faithfully with this new technology. All of the spatial harmonic math equations for the motor/generator are solved dynamically in real time, but the parameter characteristics that are plugged into the equations are informed by dynamically updating high dimensional look up tables based on the pre-calculated JMAG-RT FEA simulation (see demo movie and free trial download) that captures all the non-linearities, saturation, winding effects, etc. of the specific machine topology and construction-- right down to the material properties of the steel laminations.

Also, the speed of the simulation is critical to accurately capturing the dynamics of the switched-mode power supply (SMPS) inverter system. In this simulator, the inputs are the PWM gate command signals from the inverter control board and a 2-level, 3-leg, 3-phase inverter is included in the simulation along with the high fidelity JMAG motor/generator model and a relatively simple mechanical torque load. All of these blocks (motor/generator, inverter and mechanical load) are simulated at the same high speed rate in the FPGA.

Executing these high fidelity mathematical models in real-time requires all the computing horsepower of the most high end FlexRIO board (NI PXIe-7966R), which contains 640 mini hardcore DSPs woven into the FPGA fabric. It's like a mini supercomputer on a board and delivers up to 352 billion multiply-accumulate operations per second (MACS). Each mini hardcore DSP has a 25x18 multiplier with 48-bit adder-- equivalent to single-precision accuracy. Since these DSP cores are woven into the FPGA fabric and distributed throughout the chip, the response time from the input pins to the dynamic real-time simulation model and back to digital and analog outputs is unparalleled. Due to this unique hardware architecture with parallel distributed hardcore DSPs and ultra fast pin-to-pin response times, FPGAs are the clear technological winner for real-time simulation (and control) of power electronic systems.

The NI LabVIEW FPGA IP Builder add-on to the LabVIEW FPGA Module (currently available as an early access program) was used by NI R&D to optimize the speed and resource utilization of the simulation algorithms using high level synthesis (HLS) techniques. The idea for this tool is to enable developers to write their algorithms in high level LabVIEW graphical dataflow language without requiring knowledge of hardware description languages (HDLs), and then synthesize an FPGA implementation that is significantly more optimized than hand written VHDL or Verilog code (in terms of FPGA resources and execution speed). As I have stated before, in the future, typical high level LabVIEW FPGA code will be significanly better than hand written register level code, just as autorouters can now perform PCB layout significantly better than a person doing it without auto-routing assistance.

Here is how it works. You provide directives that capture your design constraints and help guide the LabVIEW FPGA IP Builder code generator. This can eliminate the need to perform complex manual optimizations of LabVIEW FPGA code, which was the traditional way to get the very highest level of optimization in how the LabVIEW FPGA code maps to FPGA hardware resources, but is labor intensive. The NI LabVIEW FPGA IP Builder tool uses state-of-the-art HLS technology to help you apply these advanced concepts, such as pipelining, resource multiplexing, loop unrolling, and others, to generate resource- and timing-optimized FPGA IP. With the LabVIEW FPGA IP Builder, you can match or exceed the results obtained through manual LabVIEW FPGA design optimization and focus on the high-level design of your algorithms. Because design directives are stored separately from algorithm code, you can quickly explore design trade-offs and easily enable IP reuse to meet new design requirements.

02-17-2023 05:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello NI support:

the links for this article are broken. am interested in the white paper and application links.

could you please send these docs

thanks so much, -Karl Sime

02-17-2023 05:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@ATDC wrote:Hello NI support:

the links for this article are broken. am interested in the white paper and application links.

could you please send these docs

thanks so much, -Karl Sime

I recommend you contact NI support directly

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications