- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Hi all,

I am a Sr AE from NI India.

I was recently taking a LabVIEW RT and FPGA Training after a long gap of 3 years. I realised a lot has changed in the course for good.

While I was doing a few excercises, I found that the information mentioned in the manual is slightly erroneaous.

Just wanted to check, if someone else has also found this or I have done something stupid. This is with reference to FPGA 2012 CustEd material.

Ex 7.2

The excercise is Using the Four-Wire Handshaking Protocol.

I will quote from the excercise manual

" Note The Sine Wave Generator Express VI is not supported in the single-cycle Timed Loop when compiled to run on the FPGA. The Sine Wave Generator

Express VI in the Case structure is used to simulate a signal in this exercise because you will only be simulating the execution of this VI on the development computer.

"

So I understand that this VI is suppose to run on Development system and will not give any errors. When I run this VI, I get an error that Sine wave function is not supported under SCTL hence I can't use this.

This is very misleading because the customers are asked to run this, they ll get an error and won't be able to do anything.

I found out that if you replace this with a Square wave, you can easily run this.

Could someone verify this for me ?

Ex 5.1 Timing a While Loop

The excercise is suppose to be done on a simulated hardware ? If yes, does it let us control the timing ?

I don't think it does. I followed the exact steps and was not able to do it.

I would be grateful if one of you could verify and correct me if I am mistaken about these issues.

Regards

Gautam Grover

NI India

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi Gautam,

The question related to Exercise 7-2 is a known issue already reported as a Corrective Action Request. In LV 2012, the Sine Wave Generator VI is not supported in the SCTL, but it will allow you to use it in simulation mode (execute on dev computer). However, LabVIEW 2013 will not even let you use this VI in "simulation" mode.

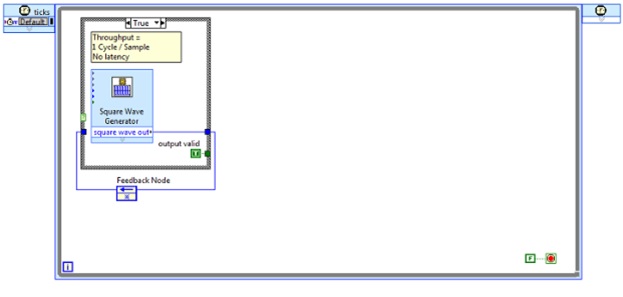

If you are using LabVIEW 2013, you need to replace the Sine Wave Generator VI inside the SCTL of the pre-built exercise VI with a Square Wave Generator VI with the "Inside SCTL" option enabled in its configuration window, as shown below:

Regarding your second question, the vi is meant to be run a simulated hardware using the development computer timing. You are configuring it this way when you right-click the FPGA target and select Execute VI on»Development Computer with Simulated I/O.

Best Regards,

CesarV

Training and Certification | National Instruments

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

I ran into similar issues running through Exercise 5-1. While all simulated indications show that the timing of the loops is the 500 ms we are requested to give it, physically it appears that, regardless of what period you give it, the execution occurs at the highest possible rate the development computer is able to do. I tried inputting 5 ms, 500 ms and 5000 ms, and the output rate in all cases appears the same, although outputs from additional indicators say otherwise.