- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Compile time when using the 9871

10-07-2014 12:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello all,

I thought that I would throw this out there as it would probably be the appropriate forum. I have a project that uses a 9871 and accesses the RS485 ports via the FPGA. When I build my FPGA application (bitfile) without the serial communication, the compile times are on the order of 20-30 minutes. With the serial ports, regardless of how many I use, the compile time is on the order of 1.5 h. Does anyone have any thoughts as to why this might be? Is there anyway of speeding this up or am I just stuck?

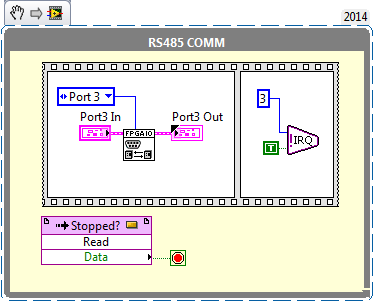

Images of the serial communication interactions are below:

Above is the high level view of the serial communication. In this, the serial port is accessed in its own loop and the user indicates a call by acknowledging the interrupt raised.

This is the view of the sub VI above. There are two cases - Read and Write - which look similar and another to handle the null case.

Cheers, Matt

10-07-2014 01:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When you have the 987x in the chassis it builds the scan engine interface to it. That is the time delta, although the increase seems larger than what I personally experience. I also have the same thing with the 9512 motion module on the chassis in the RT, not on the FPGA.

As an aside, 2014 includes the compile farm, so you could offload the build.

Casey Lamers

Phoenix, LLC

CLA, LabVIEW Champion

Check Out the Software Engineering Processes, Architecture, and Design track at NIWeek. 2018 I guarantee you will learn things you can use daily! I will be presenting!

10-07-2014 02:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, Casey. Can you explain to me what you mean by this? I explicitly use the FPGA Interface and do not have the scan interface software installed on the chassis. How exactly does the 987x "build the scan engine interface to it"? Maybe I am missing something here?

10-07-2014 02:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you have the modules on your chassis, but not on the FPGA target then it builds the pieces needed to use them without you explicitly having to create FPGA code for handling serial communication.

Chassis

987x

FPGA Target

Module

Module

Module

Let me know is this makes sense.

Casey

Casey Lamers

Phoenix, LLC

CLA, LabVIEW Champion

Check Out the Software Engineering Processes, Architecture, and Design track at NIWeek. 2018 I guarantee you will learn things you can use daily! I will be presenting!

10-07-2014 03:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

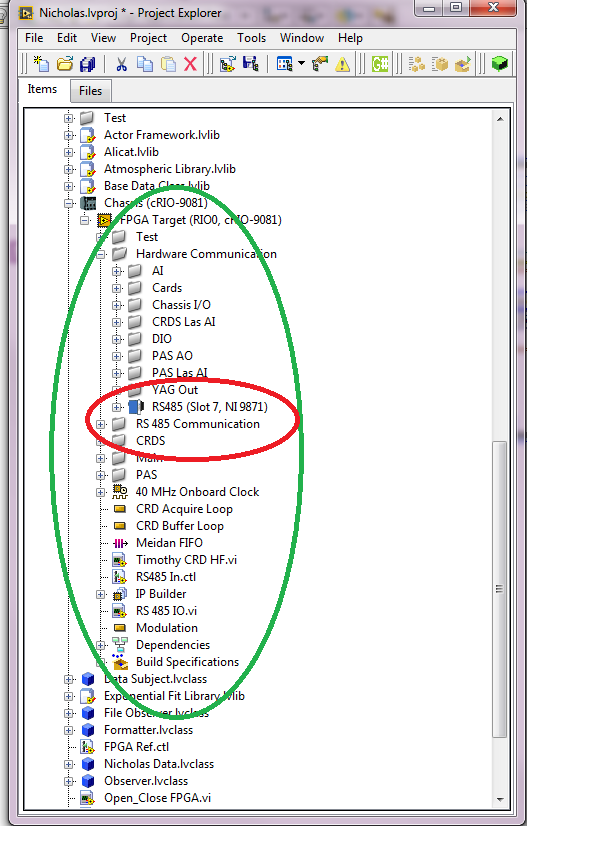

OK. No, I understand this. But, given the fact that this would use DMA if I used the scan interface (2 channels, I think), I am using this explicitly on the FPGA interface which should not use the scan interface. As you can see in the image below, the 9871 sits squarely with in the scope of the FPGA portion of the chassis, so I am not certain this answers my question. Thanks though, Casey. Matt

10-07-2014 03:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Got it.

Hopefully someone else can chime in. Not sure what resources get added automatically by putting it on the target.

Casey

Casey Lamers

Phoenix, LLC

CLA, LabVIEW Champion

Check Out the Software Engineering Processes, Architecture, and Design track at NIWeek. 2018 I guarantee you will learn things you can use daily! I will be presenting!

10-09-2014 05:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Matt,

When you drop an IO node on the diagram it instantiates logic for the compile. Some IO nodes have a very small footprint (parallel digital module) and some have a very large footprint (CAN module). I don't know that footprint for the serial module but I suspect that it may be on the larger side. If this is the case there is nothing you can do.

You can also take a look at the code and make sure it's not something you have done where you have written logic that uses a lot of resources. From the screen shot I don't see anything obvious but if you want a simple check, you can remove the module from your project and try a compile again. If it is still long then you should take a look at the FPGA best practices section and review your code.

Finally the cloud compile will help. It runs the compile on high end Linux machines and can offer a significant compile time reduction.

Good luck.