Finite Retriggerable Pulse Train with Delay for X-Series Cards

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Code and Documents

Attachment

Overview

X Series cards have a new feature that enables you to have delay on each retriggerable pulse train you want to generate.

Description

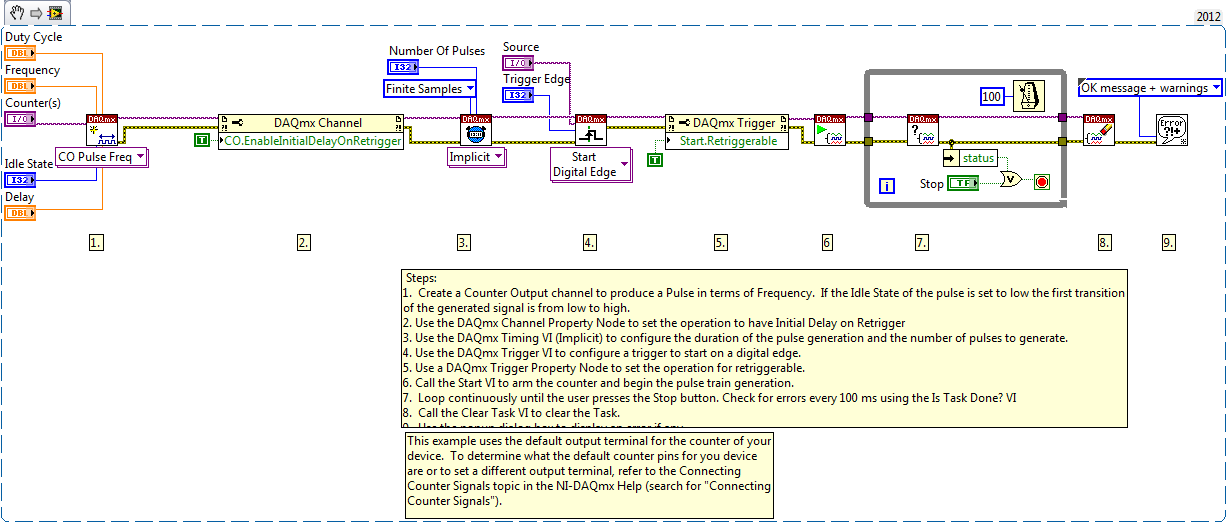

X Series cards have a new feature that enables you to have delay on each retriggerable pulse train you want to generate. X-series technology also only requires one counter to produce a finite retriggerable Counter Task, as opposed to M/E series boards which automatically allocate two counters on the board. Just by setting the Initial Delay in your channel properties, the delay will only be seen on the first trigger to start the task. By using this VI, the delay will be on every pulse train from when it receives the start trigger.

Steps to Implement or Execute Code

- Open the VI.

- Configure Front Panel for your generation task.

- Run the VI.

Requirements

Software

LabVIEW 2011 or later

DAQmx

Hardware

X Series Multifunction DAQ Device

VI Snippet

**This document has been updated to meet the current required format for the NI Code Exchange. For more details visit this discussion thread**

National Instruments

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.