Generate multiple offset PWM outputs for FPGA

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW FPGA Module

- LabVIEW Real-Time Module

- LabVIEW

Software

Code and Documents

Attachment

Description

Description-Separate-1Overview

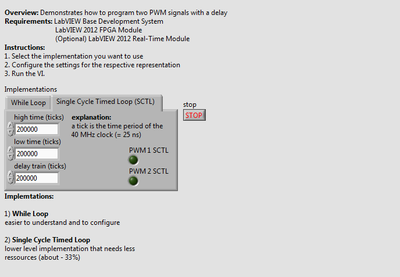

The example demonstrates how to program two PWM signals with a adjustable delay between both signals.

Description

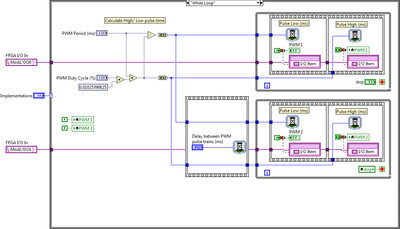

Generating multiple pulse trains using LabVIEW FPGA is relatively simple to code. In this example ('PWM with Offset.vi') two PWM signals are generated with an adjustable delay between both signals (phase shift). There are two implementations doing the same task but the 'Single Cycle Timed Loop (SCTL)' implementation is a little bit more efficient than the 'While Loop' implementation, but more low-level and a little bit harder to read.

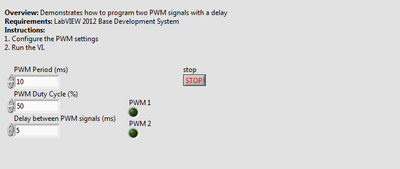

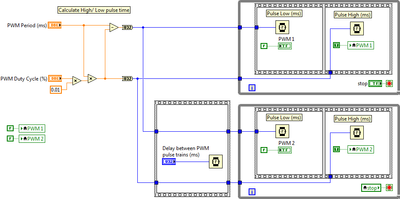

Also there is a second example ('PWM with Offset (no FPGA).vi') that only uses standard Windows LabVIEW functions that do not need the LabVIEW FPGA Module. Please be advised that this example is only for demonstration purposes and will very likely not run on a Windows system with full determinism.

Requirements

Software

- LabVIEW 2012 Base Development System (or compatible)

- LabVIEW 2012 FPGA Module (or compatible)

- (Optional) LabVIEW 2012 Real-Time Module (or compatible)

Hardware

- 'PWM with Offset (no FPGA).vi': No hardware is necessary to use this example VI

- 'PWM with Offset.vi': The example VI needs a FPGA with at least two digital outputs.

(Even though the example is meant to run on hardware the code can also be simulated, when no hardware is available.)

Steps to Implement or Execute Code

- Open the attached file

- Select the implementation you want to use

- Configure the settings for the respective representation

- Run the VI (depending on the execution mode selected it may be necessary to compile the FPGA VI to a FPGA bitfile before)

Additional Information or References

FPGA implementation

Implementation without FPGA

KnowledgeBase: Simulate FPGA Hardware Targets Using the Project Explorer with LabVIEW

Tutorial: Testing and Debugging LabVIEW FPGA Code

**The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text 'NIVerified'. Read here for more information about the new Example Guidelines and Community Platform.**

Description-Separate-2

Austin S.

National Instruments

Academic Field Engineer

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

When converting this code to FPGA, the original code gave errors as the DBL type was not supported for FPGA. I've updated the code and converted all DBL to Fixed Point data type. (9/14/2011)

Austin S.

National Instruments

Academic Field Engineer