Multi-Channel Circular Memory FFT

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Code and Documents

Attachment

This block of code is an FPGA IP that performs an FFT (64 point length in this example) every time a new data point is acquired. This block of code will perform the FFT on the past n points (where n is the size of the FFT) of a specified channel each time a new valid data point is sent to it. This IP is very similar to the Circular Memory FFT except that it extends the implementation to handle multiple channels. When using multiple channels on FPGA it's common practice to simply copy the processing block for a single channel mulitple times to perform the processing in parallel. The block diagram shown below is the type of parallel functionality described that performs circular memory FFTs on 8 different sets of data. Each random number represents a new data point on a given channel.

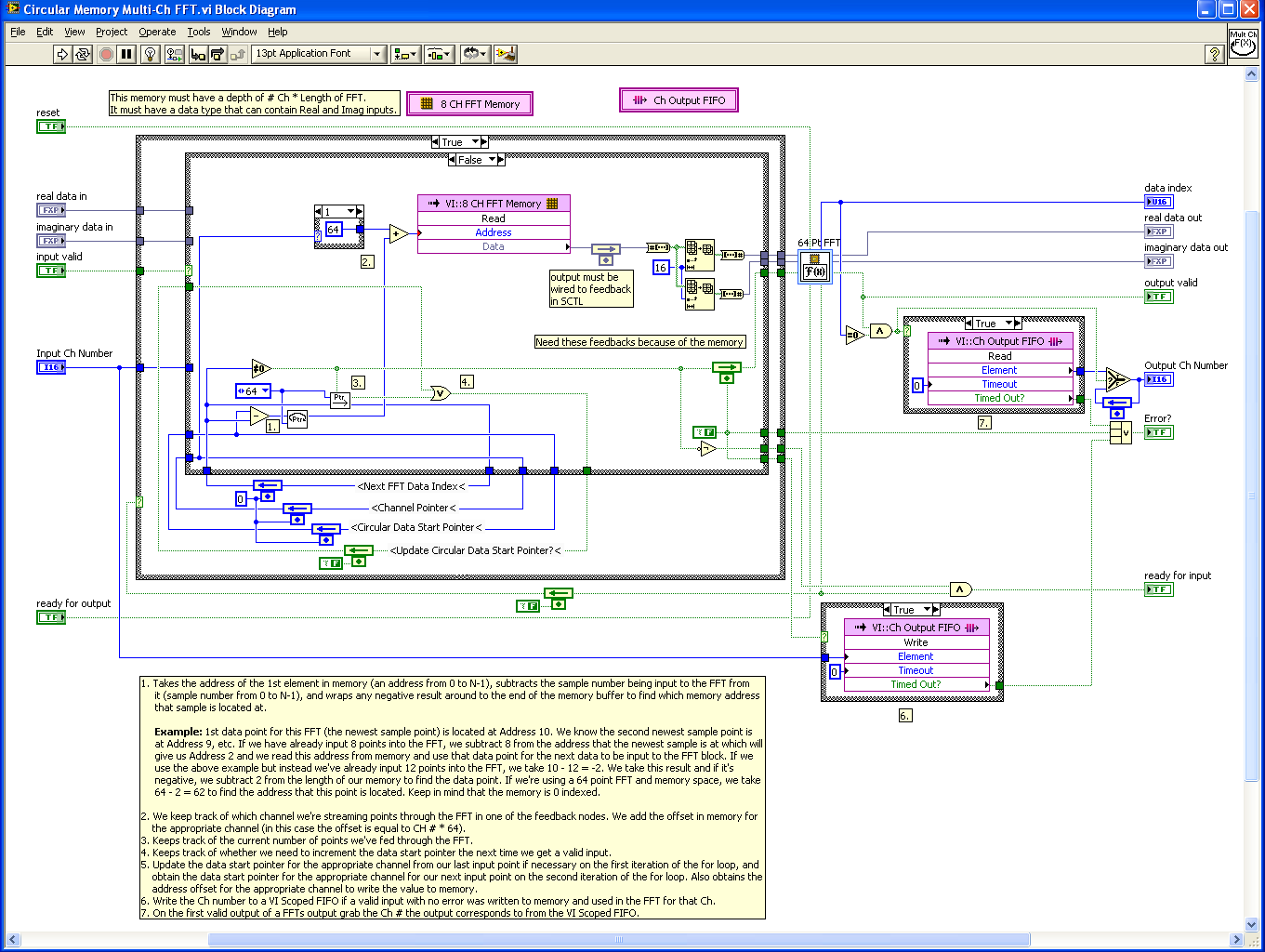

The major downfall of the above implementation is that on FPGA an FFT processing block can consume a large amount of space. If a single FFT block can run in a fast enough SCTL, each channel's data can be streamed through the FFT block one after another serially. A dataset of the entire size (or length) of the FFT must be available for each channel. The following block diagram demonstrates what this IP's equivalent functionality is in LabVIEW.

The following image shows the block diagram of this FPGA IP.

A test VI called "test multi ch circular memory fft.vi" is also included in order to test the IP in the development environment alongside the LabVIEW FFT subVI in order to compare their output.

Number of Channels: 8

FFT Size: 64

Circular Memory Size: 64 elements per channel

Forward FFT

Input Data Type: <s, 16, 1>

Output Data Type: <s, 31, 17>

Execution Mode: Inside Single-Cycle Timed Loop

Throughput: 4.07 cycles / sample

Update 4/10/09:

I updated the code for "Circular Memory Multi-Ch FFT.vi" in order to remove an unnecessary For Loop that would prevent the code from running in a SCTL. I also added "Circular Memory Multi-Ch FFT_24_24.vi" which uses the following FFT data type. This was included since I used it in example code that I'll be linking shortly.

Number of Channels: 8

FFT Size: 64

Circular Memory Size: 64 elements per channel

Forward FFT

Input Data Type: <s, 24, 24>

Output Data Type: <s, 31, 31>

Execution Mode: Inside Single-Cycle Timed Loop

Throughput: 4.07 cycles / sample

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thanks for posting! This has to be one of our first FPGA IP blocks on Community, so congratulations! Could you please rename your attachment to include the LabVIEW version number? Also, are there any similar VIs on IPNET?

LabVIEW Community Manager

National Instruments

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

I updated the code for "Circular Memory Multi-Ch FFT.vi" in order to remove an unnecessary For Loop that would prevent the code from running in a SCTL. I also added "Circular Memory Multi-Ch FFT_24_24.vi" which uses a different input data type for the FFT. I used this IP along with my Multi-Channel FFT IP in a Reference Example that I'll be posting on DevZone shortly.