SPI Slave Device in FPGA

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Code and Documents

Attachment

Description

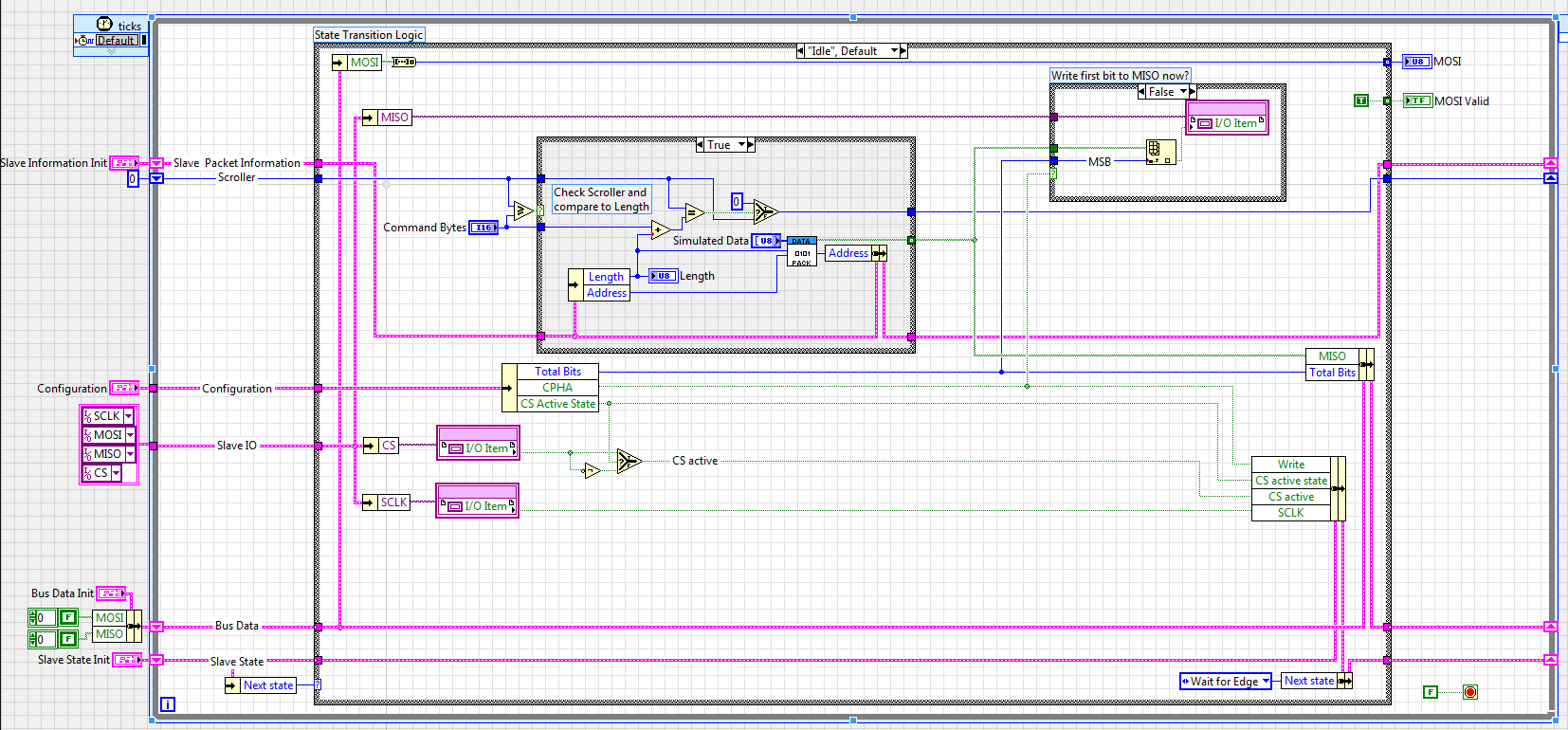

Description-Separate-1This example code demonstrates how to implement an SPI slave in FPGA that can accept variable length commands. In this particular example it accepts 3 commands: Slave ID, Memory Address to start reading, and number of addresses to read. This code was implemented on the 7833R, however the IP should work on most FPGA targets (some modification will be required). This code was tested using the NI-8451 as the SPI master and the 7833R as the SPI slave device.

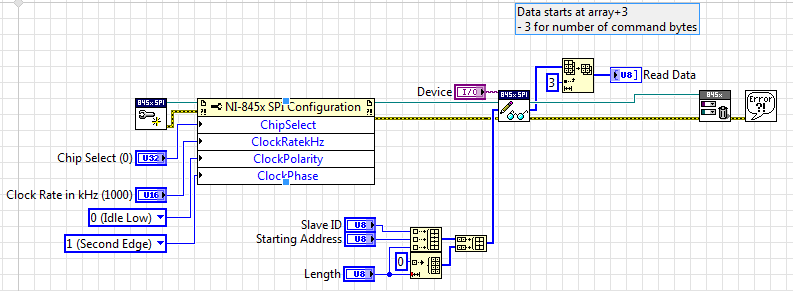

Windows Block Diagram:

FPGA Block Diagram:

Application Notes:

LabVIEW 2010

LabVIEW FPGA 2010

NI RIO 3.5

Note 1: This example doesn't use the CS Line to determine communication between master and the selected slave device. CS functionality is implemented in the commands. This example also doesn't utilize CPOL and CPHA.

Note 2: FPGA needs to be compiled for your specific target.

Useful Links:

Implementing SPI Communication Protocol in LabVIEW FPGA

Understanding the SPI Bus with NI LabVIEW

Frequently Asked Questions: NI USB-8451 & SPI

Developing Digital Communication Interfaces with LabVIEW FPGA

Description-Separate-2AES

National Instruments

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator