View Ideas...

Labels

Idea Statuses

- New 2,940

- In Development 0

- In Beta 1

- Declined 2,616

- Duplicate 698

- Completed 323

- Already Implemented 111

- Archived 0

Top Authors

| User | Kudos |

|---|---|

| 13 | |

| 9 | |

| 8 | |

| 5 | |

| 5 |

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

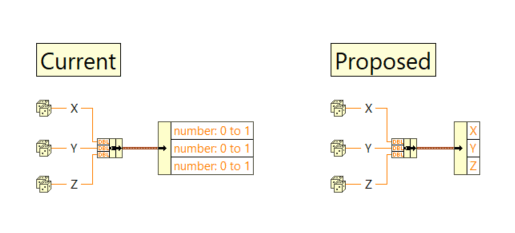

Allow Wire Labels to Dictate Name Inheritance in Bundles

Submitted by

usrfrnly

on

04-05-2023

08:45 AM

13 Comments (13 New)

usrfrnly

on

04-05-2023

08:45 AM

13 Comments (13 New)

Status:

New

Not every bundle is linked to a Typedef. It would be very useful to automatically inherit the names of previously named wires into bundles.

Labels:

13 Comments

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.