- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA_For loop inside timed loop error

08-08-2017 05:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear all

I need to transmit an array contain three elements, so I should use For_loop for FPGA_FIFO, knowing that I used timed loop when I build FPGA code an error shown that "You cannot include this function in a For Loop when the For Loop is inside a single-cycle Timed Loop."

any help!!

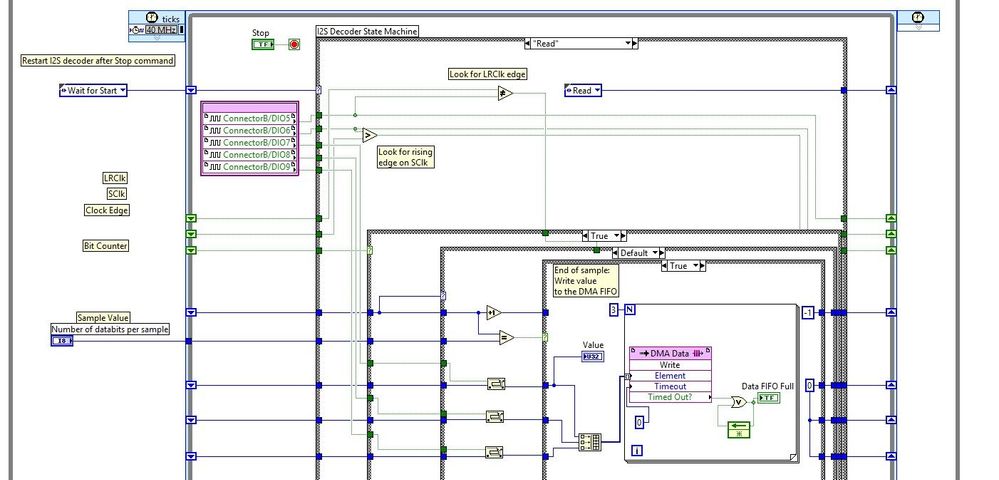

FPGA screenshot

08-08-2017 05:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

08-08-2017 06:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

They simply aren't supported as every loop in LabVIEW FPGA requires mutliple cycles to complete (except the single-cycle loop!).

For many things you might just manually duplicate the code but in your case you won't be able to as you won't be able to write multiple times to a DMA FIFO in an SCTL.

You have two options:

1. Remove the SCTL as GerdW suggests.

2. Create a new intermediate FIFO which takes all 3 elements as a cluster or similar. This writes to a standard loop which can send them sequential up the DMA FIFO in a seperate loop. This is how I have handled this case in the past if you need the SCTL (I suspect you might by the code comments)

========

CLA and cRIO Fanatic

My writings on LabVIEW Development are at devs.wiresmithtech.com

08-08-2017 06:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thank you GerdW for your reply

but in this code, timed loop is required, otherwise the code will not work correctly!!

08-08-2017 06:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you James_McN for your reply

can you help me how to represent 3 elements as a cluster then transmit data to FIFO?

because I tried that and an error appear that wires have different types.

08-08-2017 07:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

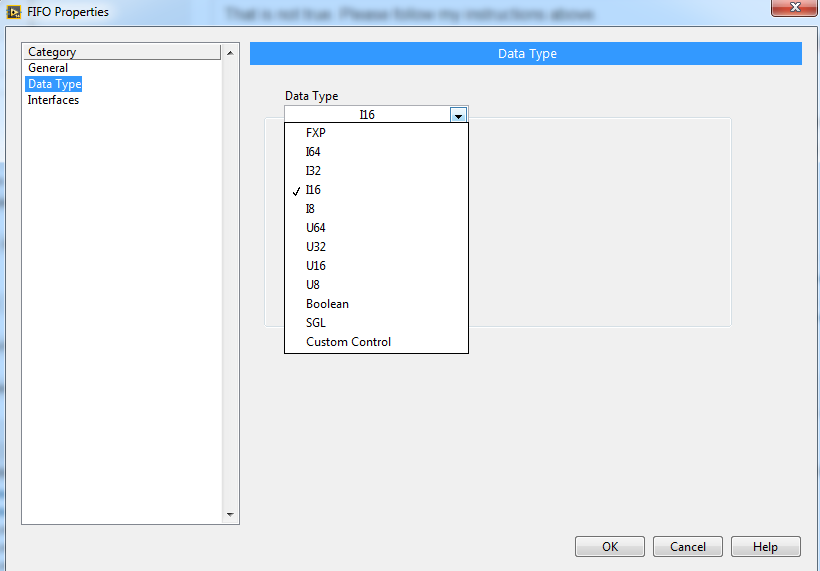

This must be a Target Scoped FIFO, please confirm that.

Create a typedef which is a fixed size 1D array of U32. Edit or make a new Target Scoped FIFO and in the datatype it will have an option for Custom Control (last one I think). Select that and then browse to this new typedef.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

08-09-2017 07:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you Terry_ALE for your reply

a Target Scoped FIFO needs For_loop, which its use not allowed in timing loop!

08-10-2017 12:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That is not true. Please follow my instructions above.

See the LabVIEW FPGA 2016 help: http://zone.ni.com/reference/en-XX/help/371599M-01/lvfpgadialog/fpga_data_type_db/

See:

- Custom Control—Opens a dialog box in which you can navigate to the custom control you want to use. This button appears only when you select Custom Control in the Data Type pull-down menu.

See image below:

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications