- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Compiler error for 9607

01-12-2016 04:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey everyone,

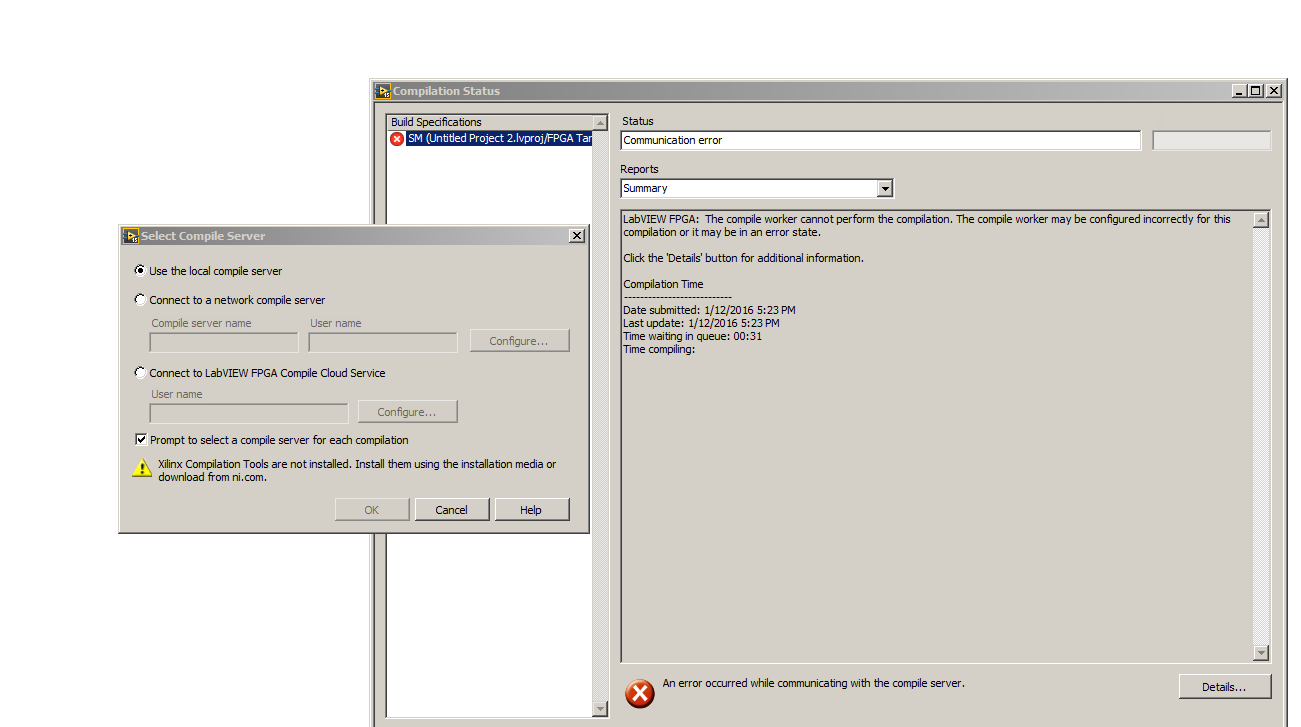

recently inroder to have a better performance of my FPGA i switched to 9607. However whne i try to comilpe the program i got error like this

my compiler works fine for 9606.

can somebody please tell me how to fix it

thank you

- Tags:

- 9607

01-12-2016 04:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you are doing local compiles, you need to instal Xilinx Compilation Tools for Vivado 2014.4.

(The sbRIO-9606 uses a different Xilinx compiler (Xilinx Compilation Tools for ISE 14.7) which I'm guessing you already have installed.)

Here are complete details on what you need to install for using the sbRIO-9607 GPIC and how to enable co-simulation with LabVIEW 2015 and Multisim 14:

The NI development tools are available for web download and fully functional 30-45 day evaluation using these links: LabVIEW 2015 HIL & Real-Time Test Suite + NI CompactRIO 15.0 Device Drivers + NI Circuit Design Suite 14.0 Full or Pro (Multisim/Ultiboard) + LabVIEW Electrical Power Suite 2015

What to install (recommended minimum set):

- LabVIEW Full or Professional. Notes: Install the 32-bit version of LabVIEW. Use Windows 7 OS. IP Builder, Xilinx Coregen and Xilinx Compile Tools for LabVIEW FPGA are not supported with Windows 8 nor Windows 8.1 (more info).

- LabVIEW Real-Time Module

- LabVIEW FPGA Module

- LabVIEW Control Design and Simulation Module

- NI RIO>NI CompactRIO 15.0 (Driver Support>Reconfigurable I/O)

- NI Multisim + Ultiboard Circuit Design Suite. IMPORTANT: When installing Multisim, select the option to install the co-simulation plug-in for LabVIEW 2014. You do not need to have LabVIEW 2014 installed. Then follow the instructions below to move the plug-ins to LabVIEW 2015 directories.

- LabVIEW Electrical Power Suite

- Xilinx Compilation Tools for ISE 14.7* Note: Needed if you are using sbRIO-9606 Spartan-6 controller for GPIC and using IP Builder, modifying Xilinx Coregen blocks, or performing local compiles. Requires Windows 7 OS. Note that new open source IP cores from NI Systems Engineering are based on IP Builder.

- Xilinx Compilation Tools for Vivado 2014.4* Note: Needed if you are using sbRIO-9607 Zynq-7020 controller for GPIC and using IP Builder, modifying Xilinx Coregen blocks, or performing local compiles. Requires Windows 7 OS. Note that new open source IP cores from NI Systems Engineering are based on IP Builder.

- Sign up for NI Cloud Compile Service: Note: This is included with NI Software Subscription Package (SSP) and a free 90 day trial is available. NI Cloud Compile Service is now included with SSP.

- Explore online training resources. Note: Online training is now included with NI Standard Service Program (SSP). Online training is now included with SSP.

IMPORTANT: Co-simulation is available and supported for LabVIEW 2015 and Multisim 14 but requires some special steps to enable it. Be sure to install the LabVIEW Control Design and Simulation Module 2015 for LabVIEW 2015. When you install Multisim 14, be sure to install the co-simulation plug-in for LabVIEW 2014. You do not need to have LabVIEW 2014 installed. Then copy the folders and files to the equivalent LabVIEW 2015 directory locations as explained below.

The trick is that, after installing the co-simulation plug in, you need to copy the folders and files below from the LabVIEW 2014 directory to the equivalent LabVIEW 2015 directory:

C:\Program Files\National Instruments\LabVIEW 2014\vi.lib\Simulation\EMI\Plugins\Multisim Design

C:\Program Files\National Instruments\LabVIEW 2014\help\msmcosim.chm

C:\Program Files\National Instruments\LabVIEW 2014\help\msmcosim.txt

IMPORTANT NOTE:

- You must keep your Multisim files and LabVIEW co-simulation VI files in the same directory path. For co-simulation with Multisim 14, the Multisim circuit design files must be located in the same directory path as the LabVIEW co-simulation VI. Otherwise a crash will occur if the Multisim file path is changed. This is a known issue that will be fixed in the future. In the mean time, the workaround is straightforward: You must keep your Multisim files and LabVIEW co-simulation VI files in the same directory path.

- To co-simulate with a Multisim 14 circuit (filename ending in .ms14) you must enter the wildcard operator, "*", in the filepath dialogue to display the .ms14 circuit files.

01-12-2016 08:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Another question is after i installed the Vivado 2014.4 my program now can go to compiled. However, i tested with a very samll program which i used to worked with 9606 (take very short time to complied), with 9607 it takes forever to generating the Xilinx IP (this step uesed to take less than 10 sec using 9606)

Could you please suggest some possible solution to this situation?

thank you

01-12-2016 10:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Check your computer's date, see if it set correctly,If everything fits, try post the log, instead of sum.

01-13-2016 09:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It is normal (expected behavior) for the compiler to spend significant time in the "Generating Xilinx IP" stage.

Keep in mind that the Xilinx Vivado compiler (used with newer targets like Zynq Kintex-7) is a complete rewrite of the FPGA compilation tools. Based on an average of various benchmark applications, compilations complete 3.5 times faster with Vivado compared to the older ISE tools. Vivado is a multi-threaded compiler which can take advantage of multiple cores. Vivado also does more advanced optimizations so applications typically take fewer FPGA resources with Vivado. (Note that it is difficult to benchmark FPGA resource usage unless the FPGA is full because the compilers will stop working if a smaller application meets timing and fits.)

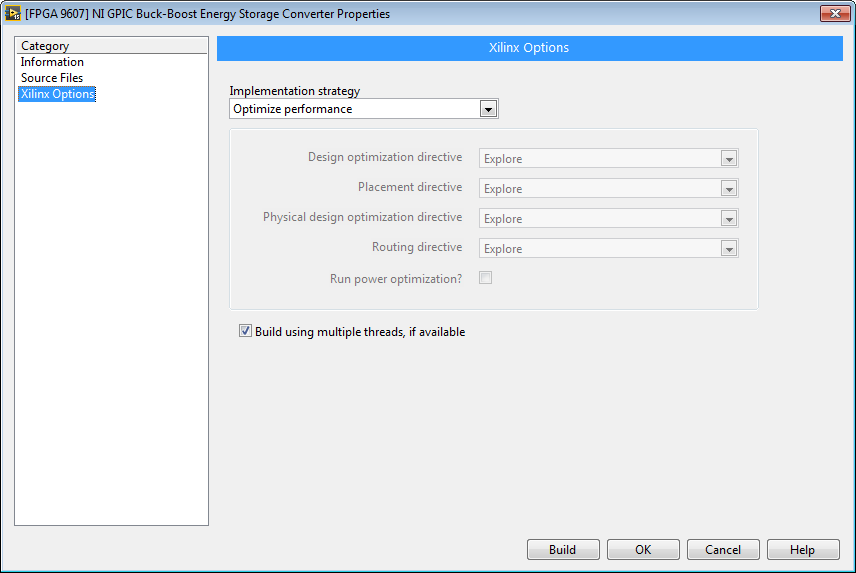

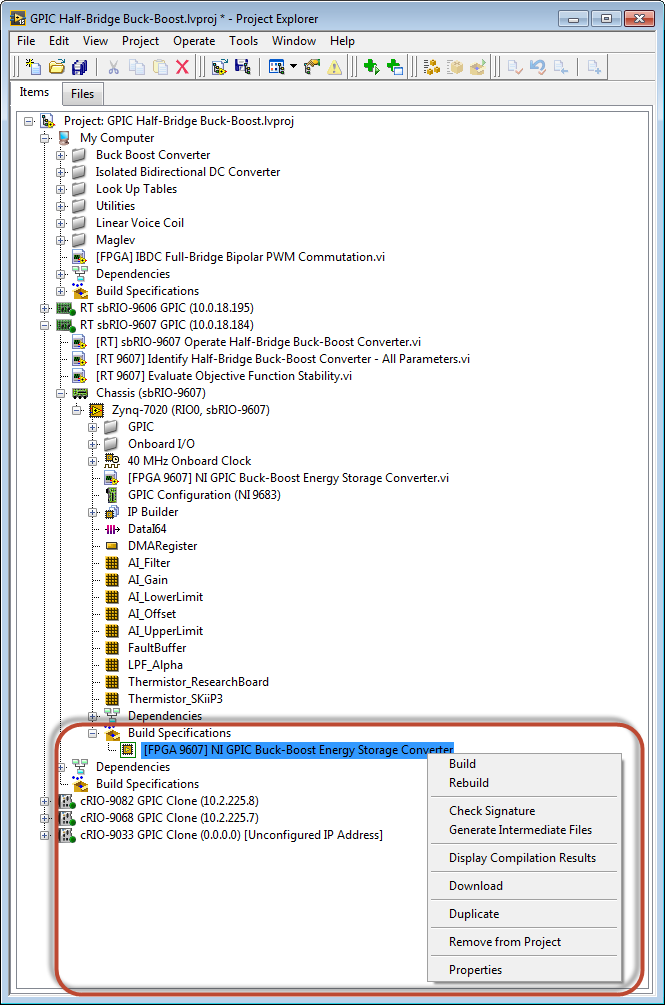

Here are the compilation settings I recommend using with the Vivado compiler. It will take longer to compile but result in more compact results and more consistent timing performance when using shared floating point math operations. Therefore, using these settings especially recommended when using my floating point toolkit (outside of single cycle timed loop) so the multiplexing of access to the shared floating point math operators is as fast as possible.

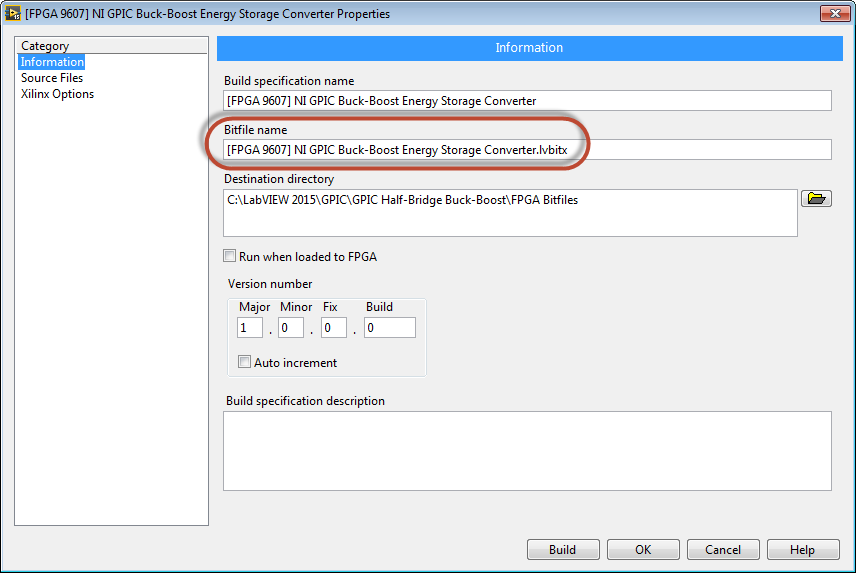

I also recommend setting the Bitfile name to match the name of your top level FPGA VI. Then point your RT application to the bitfile rather than the VI name in the FPGA Open & Run VI. This enables you to make changes to the FPGA VI in co-simulation with Multisim, while simultaneously running the RT application which points to the last compiled version of your FPGA VI. In this way, you can keep working productively on code improvements while compiles are happening. By doing this, I don't really worry about compilation time because it doesn't slow down my development progress much at all.

All of these compilation settings are accessed by right-clicking on the FPGA build specification and going to Properties.

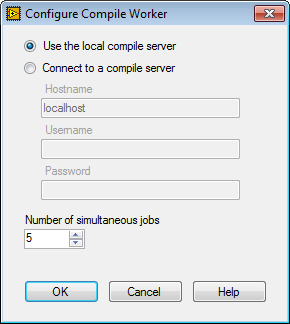

Additionally, you might want to set up your local compile worker to run multiple compilations at once. To do this go to the Start menu and type "FPGA Compile". Then open the FPGA Compile Worker and click on the Configure button. Set the number of simultaneous jobs to the desired value as shown below. The number of simultaneous jobs your computer can handle depends on how much RAM memory you have installed. You need to shutdown the compile worker to apply the changes.

One last thought- have you tried out the LabVIEW FPGA Cloud Compiler? I worked with NI leadership to get it included at no extra charge with the LabVIEW Software Subscription Package (SSP), so if you have SSP on your development toolchain you can use it for free. If you don't have SSP it can also be purchased and there is a free trial available. Regardless, you can follow the link below to get access to it.

Sign up for NI Cloud Compile Service

Note that the Cloud Compile Service is not necessarily faster than compiling on your local machine, but it does offload the work so you can put your computer to sleep while the compilation is running and reconnect later. Also, it makes it easier to run multiple compilations at once.

I hope this is helpful information and that you come to enjoy the very latest and greatest FPGA compilation technology from Xilinx and NI. Best regards! -BMAC

01-13-2016 11:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey

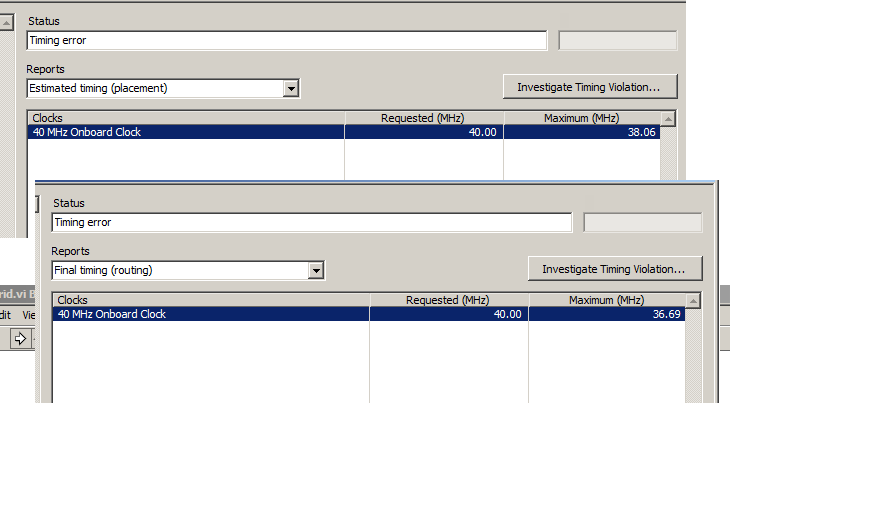

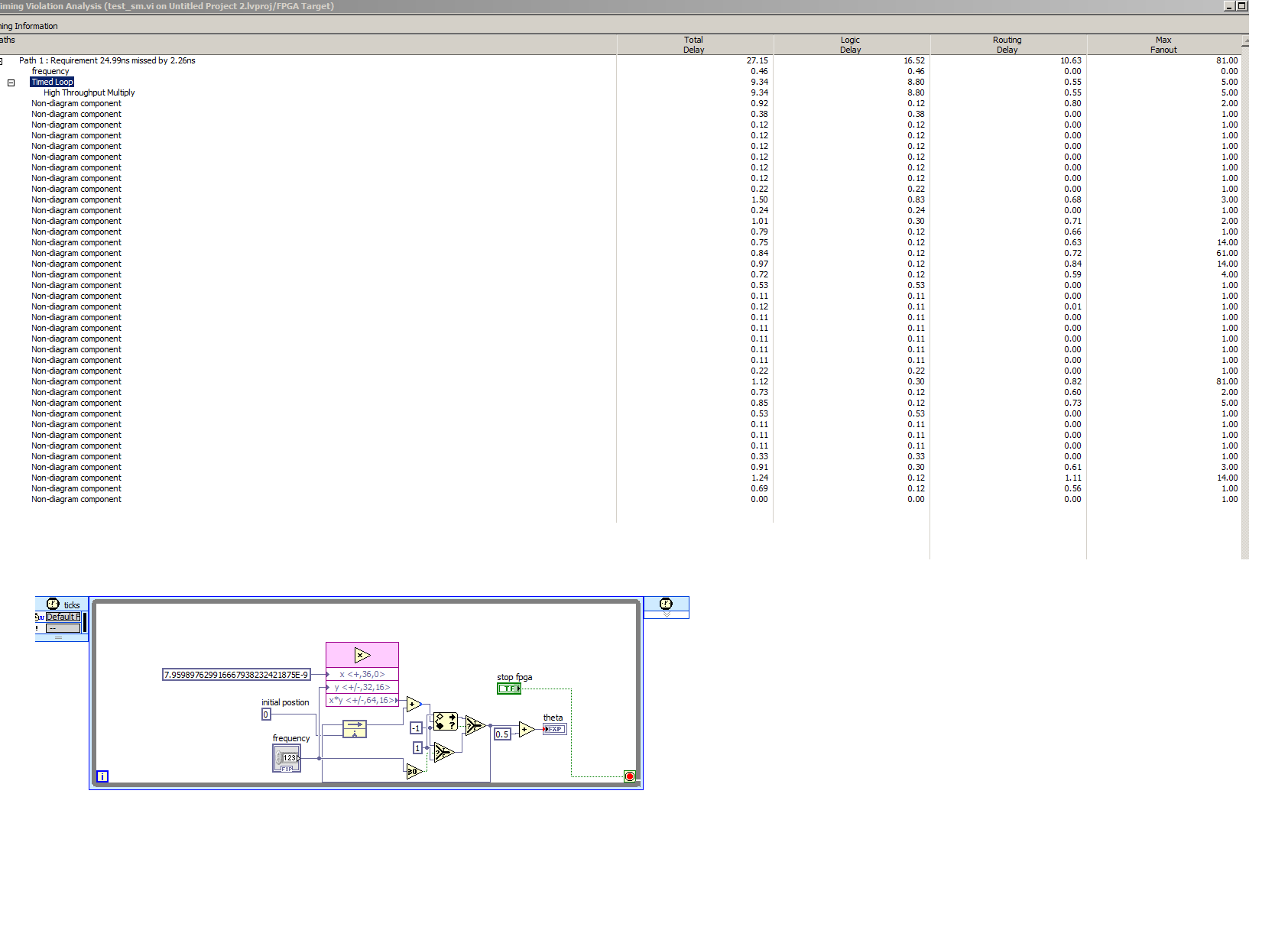

i set the xlinx complier build specification as shown in the pciture. However a same project which can be successfully compiled in 9606 get timming error in 9607

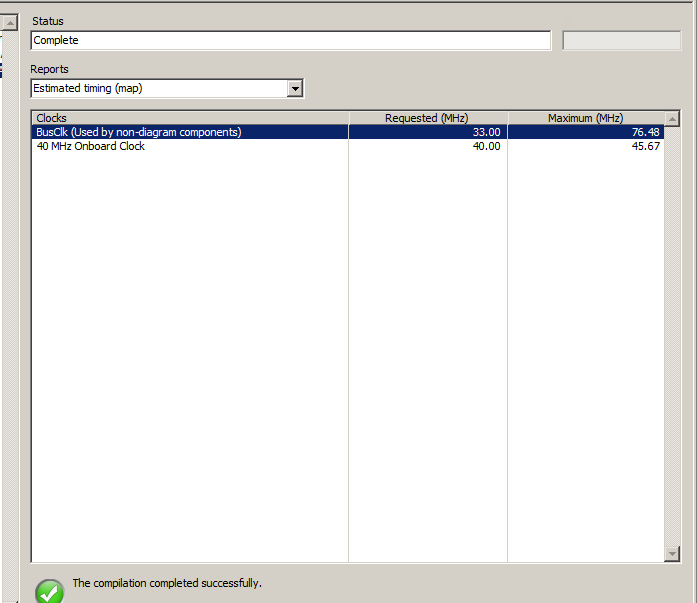

In 9606 the estimate timing result is

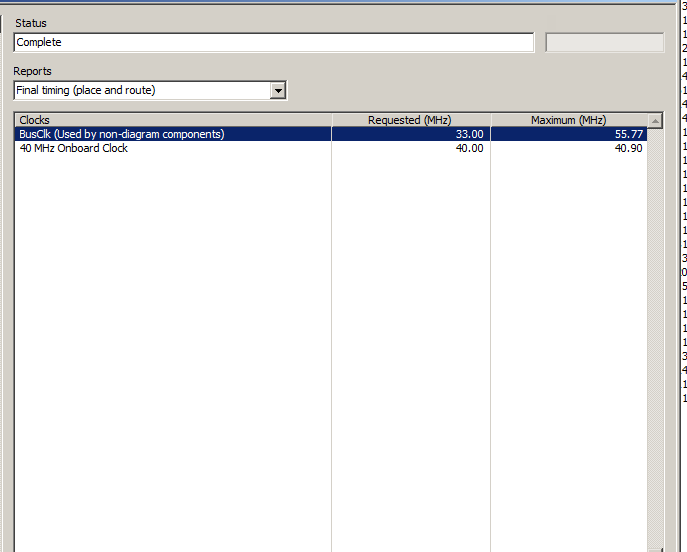

the same program copy from 9606 get timming like this

and we can tell the busclk in 9606 is also gone

i checked the timming error one is a high throughput multiply in timed loop but i have the same in 9606

can somebody tell me the reason

01-13-2016 12:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Click the Investigate Timing Violation button and look for any non-negative timing values that indicate a violation. Attach a screenshot. Then double click to see which code is causing the violation. Attach a screenshot of the block diagram. Then we can help you find the source of the problem.

01-13-2016 01:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

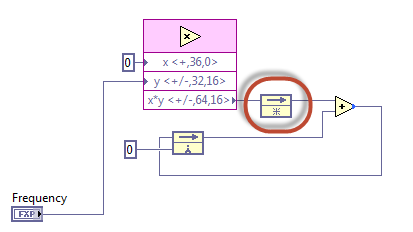

the picture shows the error list and the loop which casue the error, agian it has no problem in 9606

01-13-2016 01:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

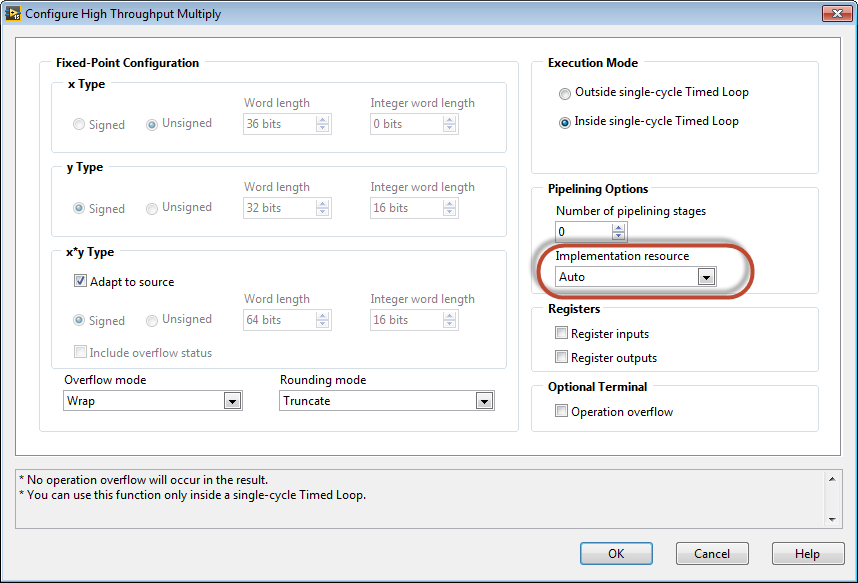

Here is what is happening: Your loop was barely meeting timing on the sbRIO-9606 controller because you have a lot of math and logic after the high throughput multiply, which is contained in a single-cycle timed loop (SCTL). The SCTL requires that the compiler completes all of the math on every clock tick of the FPGA (typically 25 nanoseconds). Generally speaking you should always include a feedback node after each high-throughput math operation so the other math operations are executed in parallel, rather than sequentially. That's because it is common for multiply, add, subtract math operations to take a large portion of the 25 nanoseconds available, therefore adding more math in series without pipelining will commonly cause a timing error.

Just to be clear on what I mean, I've recreated part of your code and added the feedback node where it needs to be.

So why would the timing pass on the Spartan-6 FPGA and Xilinx ISE compiler of the sbRIO-9606 and not pass on the Zynq-7020 FPGA (which has faster fabric) and Xilinx Vivado compiler? There are many reasons this may be the case, such as differences in the compile optimizations, routing/timing, etc. Another is that the compilers may be assigning different hardware resources to implement the math operation- for example, one compiler may be using a hard DSP core while another is using look up tables (LUTs). You can indicate your preference for what resource is used in the configuration panel under Implementation resource. Keep in mind that look up tables are faster in some cases, depending on the size of the fixed point word lengths for inputs and output.

01-13-2016 05:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

the problem sovled after i placing the feedback node.

thank you