- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DSP 48s

10-19-2015 09:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey everyone

I'm using GPIC doing a induction motor control. In order to make sure the code work, I compile it step by step. Now I’m very closed to the end of the control however, I used 57 of out 58 DSP48s in the FPGA. Which I think is too much.

What kind of certain function would cause this usage and is there a certain way to reduce the usage of the DSP48s fpga resources?

Thank you

Regards

Jia

10-24-2015 09:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You should attach your code...

10-25-2015 03:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Actually, using all of the DSP cores embedded in the FPGA fabric is typically considered a good thing, since it enables you to obtain the full embedded computing performance-per-dollar of the device.

Unlike reconfigurable logic fabric slices, there typically are no compilation problems (such as difficulty in meeting timing requirements) associated with utilizing all of the hard core DSP48s. I'll explain in a later post how you can manage DSP core usage in your LabVIEW FPGA code, but first some background info...

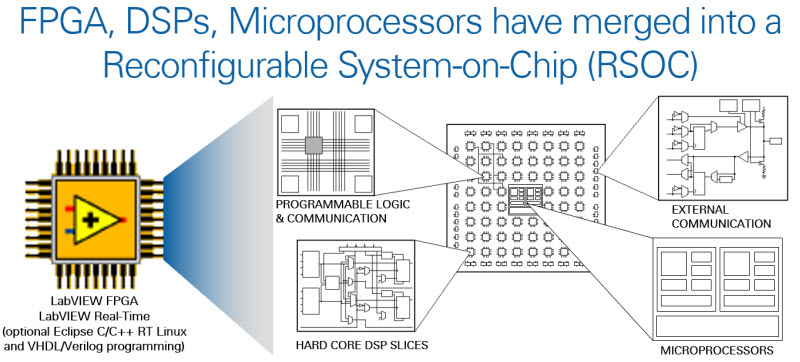

Here is a diagram showing the architecture of these modern Reconfigurable System-On-a-Chip (RSOC) devices like the Zynq-7020 on the new sbRIO-9607 control board for the GPIC (which contains 220 DSP cores, two ARM microprocessors, and 85,000 programmable logic cells). The previous generation sbRIO-9606 control board for GPIC has 58 DSP cores, an external PowerPC microprocessor, and 44,000 programmable logic cells. (Don't worry the sbRIO-9606 will be orderable for many years to come because NI has a standard 10 year active/mature + 5 year maintenance lifetime support policy for NI RIO embedded systems.)

A good question to ask is how much embedded control algorithm and signal processing performance can be achieved using these embedded DSP48 cores, and how does it compare to conventional monolithic DSPs often used for power electronics? Here is a table with my calculations:

| Vendor/Part | Description | MMACS* per Chip | Digikey Price ($) | MMACS/$ | Watts/Chip | MMACS/Watt |

| TI TMS320F2808 DSP1 | C2000 DSP, 32-bit, 100 MHz, fixed pt | 100 | $15.43 | 6.48 | 0.55 | 182 |

| TI TMS320C6203B DSP2 | C6000 DSP, 300 MHz, fixed pt, dual multiplier | 600 | $85.92 | 6.98 | 1.05 | 571 |

| Xilinx Spartan-6 LX45 FPGA3 | FPGA, 58 DSP48A1 multipliers at 250 MHz, 44K logic cells | 14,500 | $52.00 | 278.85 | 2.46 | 5,897 |

| Xilinx Zynq Z-70204 | Zynq-7020 All Programmable SoC, 220 DSP48E1 multipliers at 250 MHz, 2 ARM processors at 667 MHz, 85K logic cells | 55,000 | $113.89 | 482.92 | 3.2 | 17,188 |

* MMACS = Million Multiply-Accumulates per Second (a measure of embedded computing performance)

1. The TI TMS320F2808 DSP computing performance (MMACS per chip) is based on the manufacturer stated value.

2. The TI TMS320C6203B DSP computing performance (MMACS per chip) is based on the manufacturer stated value.

3. The Spartan-6 LX45T computing performance is calculated as follows: 58 DSP cores performing multiply-accumulate operations at 250 MHz = 58*250 = 14,500 MMACS. Note that this is a low estimate because it ignores the computing performance of the programmable logic cells.

4. The Zynq-7020 computing performance is calculated as follows: 220 DSP cores performing multiply-accumulate operations at 250 MHz = 220*250 = 55,000 MMACS. Note that this is a low estimate because it ignores the computing performance of two ARM microprocessors and the programmable logic cells.

Based on the table above, the performance ratios between the conventional C6000 DSP and Reconfigurable System-On-a-Chip (RSOC) FPGAs used in the previous and current generation NI General Purpose Inverter Control (GPIC) systems are listed below.

Performance Ratio (Spartan-6 LX45 / C6000 DSP) | Performance Ratio (Zynq-7020 / C6000 DSP) | |

MMACS per Chip | 24 | 92 |

MMACS per Watt | 10 | 30 |

MMACS per Dollar | 40 | 69 |

The way Moore's Law has progressed in recent years is to incorporate more and more

parallel computing elements into a single integrated circuit, thereby driving up the performance-per-dollar. It is remarkable that the latest reconfigurable system on chip (RSOC) devices include so much parallel computing capability that they achieve orders of magnitude higher performance per dollar. In the case of the Zynq-7020, it achieves 69 times higher performance per dollar than a traditional monolithic dual core DSP. That is a 6900% improvement.

But what is the impact for teams designing industrial equipment that utilize RSOC technology? It means being price competitive while delivering more capabilities and features that serve the customer better. It means utilizing that computing power for features that enable the equipment to perform more reliably in the field and for longer, making it more user friendly and safe to operate, achieving higher performance and quality, supporting equipment deployed remotely better, delivering new features and benefits through software updates, getting to market sooner in response to new customer requirements, and being a more efficient and productive design team.