- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Help needed with three phase pll to measure 60 HZ frequency

08-04-2015 10:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Make sure the 3-phase voltage signals are connected in the correct phase sequence. In other words, Vab should lead Vbc by 120 degrees, and Vbc should lead Vca by 120 degrees. Create an RT app to view the waveforms and check this.

08-04-2015 11:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

HI BMac,

Yes, they are well connected I have already checked it, yesterday my PLL was locking the frequency with some error but I made some changes and then it stopped locking, I used x/A for PLL gain.

My another program for frquency is running well, i shared the memory and tracked the frequency for half of the cycle. connection to my FPGA are fine. I wanted to use this programe which was discussed here.

I have attached a code and kindly have alook at it.

thanks in advance.

best regards

Arv

08-04-2015 12:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Arv,

From observations, the following changes in the code might be helpful.

1. Remove the flat sequence stucture, because it is not necessary.

2. You do not have to multiply the inputs. I am assuming you are performing this to account for the voltage step down. You should do this multiplier after the RMS block (Which you are doing in the right way)

3. Also, when you are performing this multiplier, you are multiplying a fixed point data type with a 16 bit integer. I am not sure if this causes any issue. Avoid this multiplication.

Also, try to play with the gain values for the PLL block.

Regards,

Kumar

08-04-2015 01:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi kprabaka,

Thanks alot for respying me. I used these multilpliers just to give a gain to the input signal to the PLL as BMac suggested that, it should be around 100 for PLL fuctioning.

I will take these multiliers out. I played a lot with gain but couldnt get success. Yesterday, I was giving gain to PLL and it worked but aftera while i made some changes, and it lost again.

kindly help me in suggesting the PI gain to PLL block.

I set my PLL with proper data what you suggested in the discussion and it worked, but now its not working.

Hope to hear from you soon. It would be great if you could share your vi code with me.

thanks.

best regards

Arvi

08-04-2015 01:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

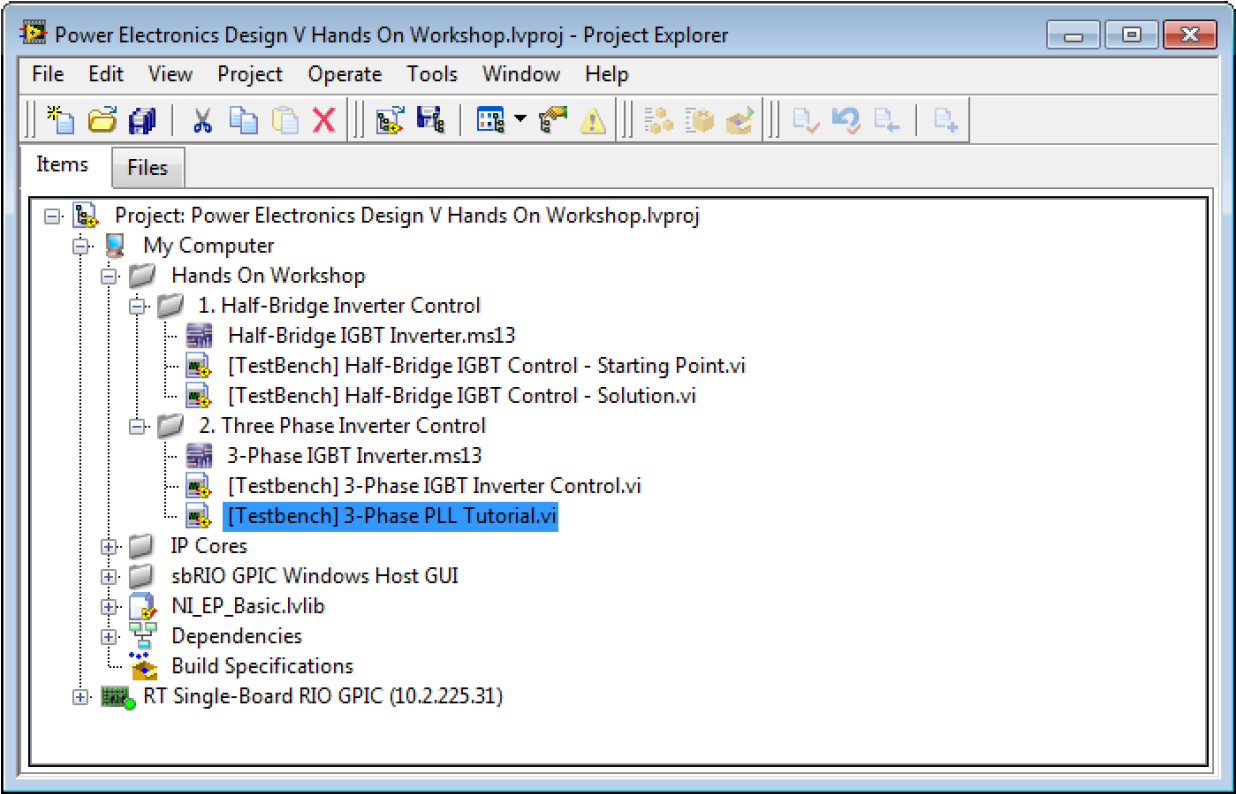

You may also find helpful the 3-phase PLL co-simulation based training examples in the Power Electronics Design V Training Course material. See Module 2, Exercise 1 on Understanding the Phase-Lock Loop (PLL), beginning on page 41 of the training manual PDF. The training also covers the tuning of the PI controller.

NI Power Electronics Control Design V Training Course

You may want to run those examples and compare the code to yours in order to root cause the problem you are seeing.

- « Previous

-

- 1

- 2

- Next »