- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Communication with USRP X310 via 1 GigE and 10 GigE

03-16-2021 01:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

- Hi all

- I need to add customized fpga code with ettus build fpga image "USRP_X310_FPGA_HG " using labview fpga

- From where can i get the labview fpga source code for the above mentioned ettus build fpga image so that i can customize this code as per my requirement

03-17-2021 02:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

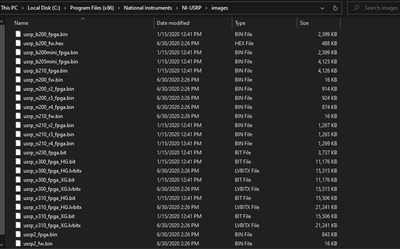

As I understand, you are looking for USRP LabVIEW default images. If so, you could find the images after NI USRP driver installation basically by this path C:\Program Files (x86)\National Instruments\NI-USRP\images. For image modification LabVIEW, LabVIEW FPGA, and NI USRP drivers are required.

05-01-2021 10:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

The images provided with USRP hardware driver are just bit or lvbitx files. I need FPGA code for these images so that i can add some customized blocks with that code.

05-03-2021 01:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

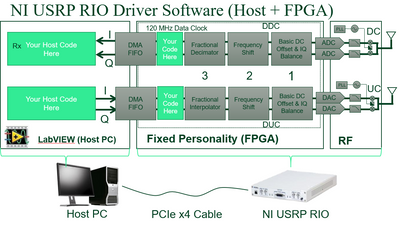

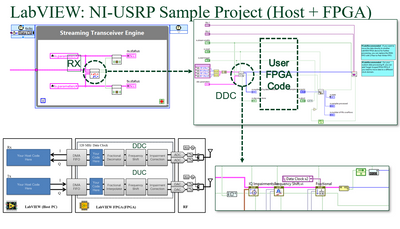

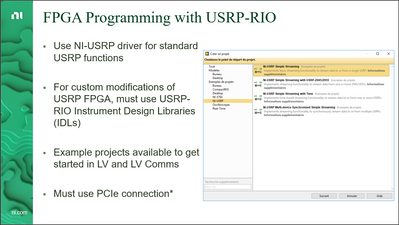

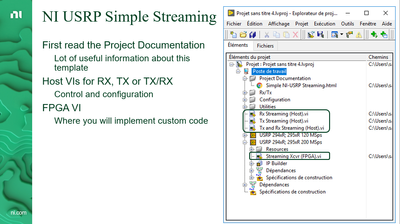

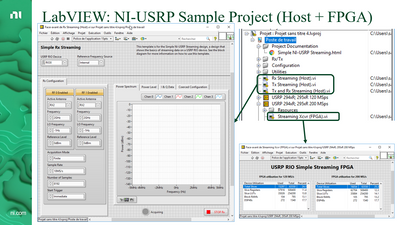

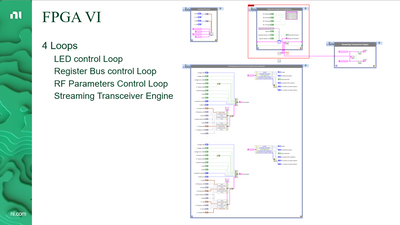

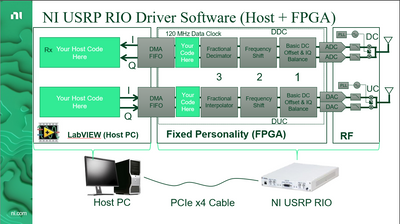

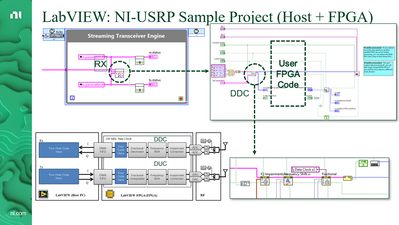

for LV it is possible to modify the FPGA code in LV FPGA. The MXI connection for FPGA modification is mandatory. The mentioned default lvbitx files could be modified in LV using the FPGA module (See below).

If the modifications could be done in Vivado from Xilinx, ISE from Xilinx, GNU make, I will suggest using this link and follow Generation 3 instructions.

best regards

05-03-2021 12:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Sivolenko Thank you so much for your kind comments.

1. The pictures you added are the sample FPGA project provided with the NI-USRP drive.

2. Yes you are right that we can modify FPGA Code given in the sample project.

3. I need the Labview FPGA source code of the image "usrp_x310_fpga_HG.lvbitx" provided in the NI-USRP dirver images folder.

4. This is just the complied bit file that can be loaded on USRP FPGA using MXI. I have loaded this bit file in USRP X310 and tested with the host examples provided with NI-USRP driver using 1 GigE and as well as with 10 GigE, and it works fine.

5. Now I need the Labview FPGA source code for this image (usrp_x310_fpga_HG.lvbitx) so that i can add my customized block with it because it is tested code.

Hope i explained my issue.

05-12-2021 05:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Idrees,

the default LV images are coming with the driver. You need to modify the default FPGA image in the images folder, compile it with your custom code and load it on USRP.

Thank you for the details.

05-14-2021 10:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

the default LV images are coming with the driver. You need to modify the default FPGA image in the images folder, compile it with your custom code and load it on USRP

i have found the fpga images in the directory "C:\Program Files (x86)\National Instruments\NI-USRP\images".

These are just *.bit files and *.lvbitx files.

How can i modify these images in labview??

05-17-2021 06:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

to modify the FPGA code in LV FPGA the MXI connection is mandatory. The mentioned default lvbitx files could be modified in LV using the FPGA module. Also the RIO API is required as well. Please follow below mentioned instruction:

and compile the code.

Hope this will be helpful.

02-07-2024 07:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

After compiling the file, do we need to write the newly generated bit file separately to the USRP using the NI-USRP configuration Utility ? Or it will be downloaded automatically when we run the host VI. I am using NI USRP 2954.

02-07-2024 07:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi there,

Yes, the reimaging is mandatory as the USRP is keeping the older image on flash.

Hope this was useful.