- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA code cloning for multiple modules

Solved!08-02-2023 07:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi All,

I would like to ask you for your advices, approaches and best practices for FPGA/RT code.

Situation: I implemented cRIO FPGA code for one high speed DIO (Manchester coding and decoding with buffering data to transmit and received data buffering from UUT (using few independent While Loops and FIFOs to pass data between loops)). Controls and Indicators are used to send and receive data between FPGA to RT.

Problem: How FPGA code and controls between RT to FPGA should be done when I want to add another DIO module for 2nd UUT, or when I want to add 7 DIO modules and coding and decoding 8 UUTs.

It is not problem to copy and past FPGA main code 8-times (it will not fit on one screen) but number of FPGA controls and indicators will be too high (in RT Read/Write control).

I could imagine to use one set of controls and indicator + module id and one FPGA loop which will distribute controls/indicators values to individual modules with help of FPGA Registers or FPGA Memory. Then DIO I/O Node references, FPGA Registers/Memory references will be passed to individual module subVIs as constant references from Main FPGA VI.

Or is there some nicer way to do it.

Or is there demo/template which I didn’t find.

Thank you for your time.

Best regards

Peter

Of course FPGA code must be recompiled after adding more modules.

Solved! Go to Solution.

08-03-2023 11:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, that is the case where Instruction Framework fits very well.

https://forums.ni.com/t5/NI-Labs-Toolkits/Instruction-Framework-Tutorial/ta-p/3533500

Instruction Framework is used in various NI software components, such as USRP Sample Project, HSSI/REOSC IDL, VST (FPGA is not open anymore). But it can be also used CompactRIO, and any other NI FPGA hardware.

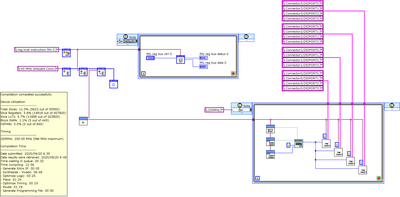

Below is an example of 128Ch PWM generator by PXIe-7822 based on Instruction Framework. DIO lines can be replaced with the ones on C module such as 9401. There are only one control and two indicators on FPGA VI front panel.

08-04-2023 08:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you,

Something like this I was looking for.

Peter