Inactive

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

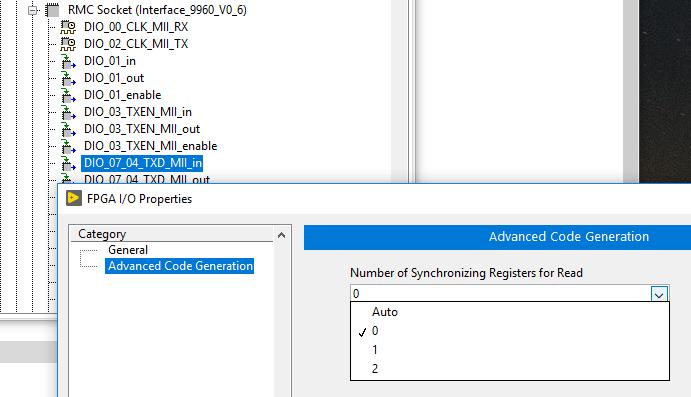

RMC Socket Number of Synchronizing Register

Hello,

Is there any possibility to use a dedicated file to change the Number of Synchronizing Register

Today we need to right click on the DIO + Propriety + Advanced Code Generation + Select Nb of register.

On a SBRIO 9607 I have to do it 96 times and if I change something with the CLIP generator I need to do it again.

In my design I use VHDL IP so the synchonisation is already done on the VHDL and I don't need extra clock.

I try to edit with Notepad++ the .lvproj file and change the NumberOfSyncRegistersForReadInProject or NumberOfSyncRegistersForOutputData but it's not clean...

If you have an idea it will save a lot of click.

Thanks

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.

Hi Manu,

Sorry for the delay. We had some conversations here about this. I agree this is painful, and is something we are looking at simplifying in general and for NXG too. It might not happen immediately.

There might be work-arounds possible in the short-term. We do think you might be able to write a script that modifies the lvproj. You could probably use G scripting to edit the loaded project as well, but a python script that runs on a saved lvproj should do the trick. This is not something we tried so I am not sure if this would end up being a big time sync for you, but something to consider. Might not be super elegant.

This post might help too, I think there is an RMC CLIP generator that you can use: https://forums.ni.com/t5/Hardware-Developers-Community-NI/sbRIO-9651-SOM-IO-Interface-and-CLIP-Gener...

Also I think you can use the IO in groups of 32 so there are fewer IO items that need to be modified.

I realize this was more of an "Idea Exchange' thing than a forum post but I figured this could help!