- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can't make RT use generic FPGA FIFO

03-19-2015 02:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

On a cRIO, I'm making a TCP server in RT that feeds data to a DMA FIFO for FPGA consumption. We are setting up multiple servers where each feeds a different DMA. (No, I don't want to merge and multiplex to single DMA).

I want a single RT program that takes a FIFO reference so that I can reuse the same RT code for different FIFOs. I can define a FPGA FIFO reference control,

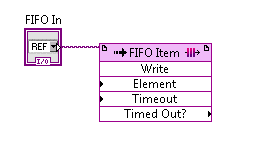

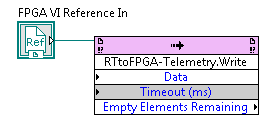

but this only supports writing a single element at a time (or two on our target if you select peer-to-peer streaming for the FIFO). I have tuned the RT program for performance, and looping over thousands of elements per second in RT is NOT the solution. I want to use the "other" FIFO write which supports arrays - the one I can reference from an FPGA reference as follows:

However, using the FPGA reference I believe requires a particular named FIFO - therefore tying the RT code to a particular FIFO.

Any ideas how to do this?

Steve

03-19-2015 03:58 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey maherhome,

One thing to clear up, the first code snippet you showed will only work on the FPGA (and the 2nd snipped is host only). Not a big deal, since you want to use the right one anyway, but I wanted to be clear that the API is a bit different between host and FPGA.

As for a solution, to your problem, I think the LabVIEW FPGA Advanced Session Resources NILabs release will do what you are looking for.

Thanks,

Sebastian

03-19-2015 05:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As speleato said, if your FIFOs have different names then you need to use the Advanced Session Resources. Be aware of the known issues though - it doesn't work very well for remote targets (e.g. over ethernet).

03-19-2015 07:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

^^although its worth pointing out that rio does work over the network, so if all you're doing is TCPing things directly into a fifo you may be able to save yourself some time and effort letting RIO do the work for you.

03-20-2015 06:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry about the mis-targeted code snippet - I was playing around with FIFO things on a block diagram and didn't noticed the error.

The Advanced Session Resources looks great. I've downloaded and will look into it.

I'm intrigued by the "let RIO do the work for you". Is this referring to using Labview on PC and a network shared variable (or whatever the name is) and then have an RT program on the cRIO stuff the variable contents into the FIFO? We don't have Labview on our remote device; hence the raw TCP setup. Or is there something else (hmm, I don't think you can use nidaq-mx to talk to cRIO) ...

Thanks!

Steve

p.s. the Giant Tetris looks cool!

03-20-2015 10:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I believe smithd is referring to the fact that the Open FPGA VI Reference node can open references to RIO devices located on the network. This means that it's possible to call the FIFO Read operation on the remote system. This also works with the FPGA Interface C API, so while the RIO Driver is required, you don't actually need LabVIEW on the remote system either.

A couple cautions if you decide to pursue this. Firstly, the remoting protocol is not optimized for streaming performance. So depending on your needs it may or may not be adequate. Secondly, the server is single threaded, so reading multiple fifos concurrently can result in timeouts and/or larger than expected latency.

03-20-2015 02:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

All,

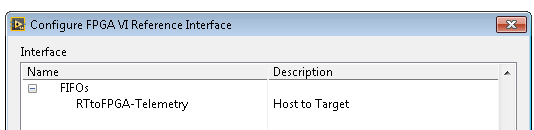

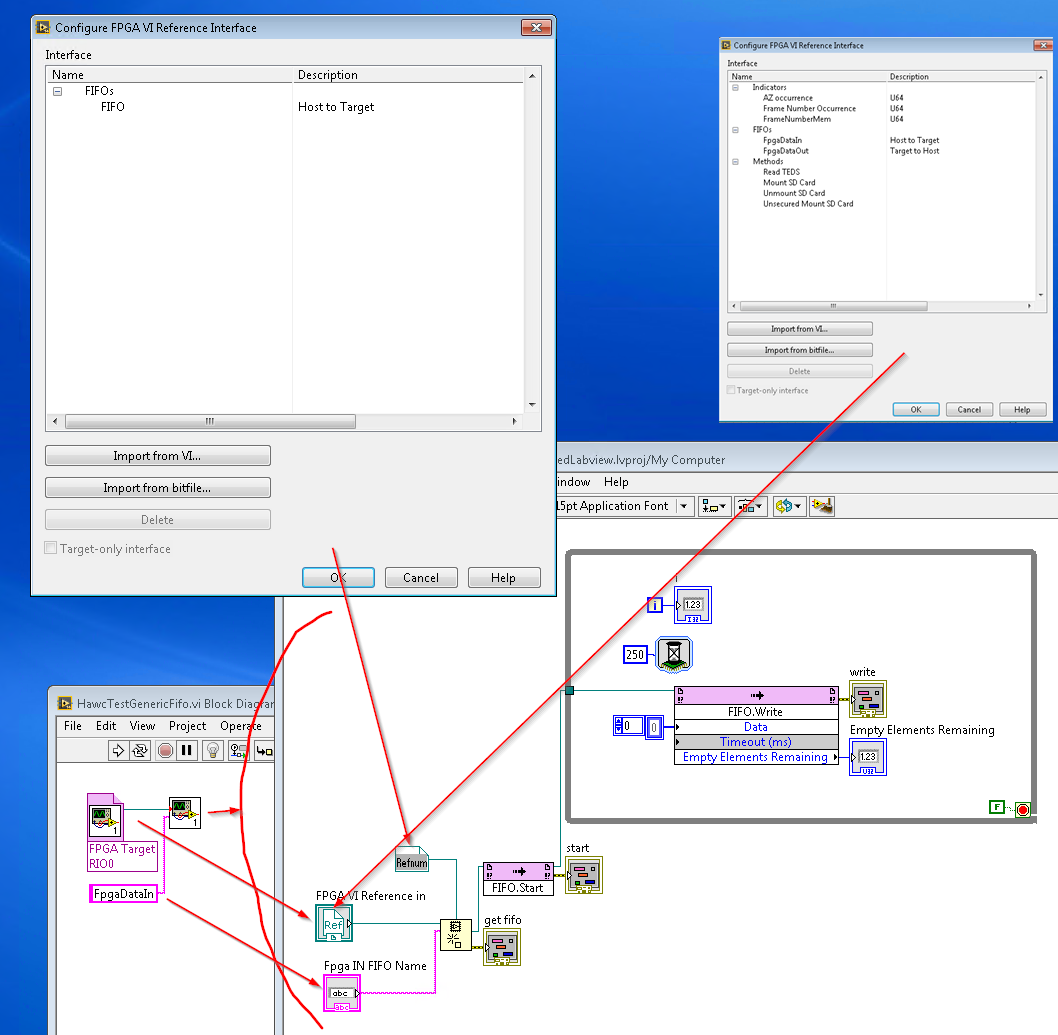

Thanks for the advice. I'm trying to create a basic test using the Advance Sessions Sources and am getting a FIFO name error (-61206) from the Get Single Resource Session node. The messy diagram below is showing the test VI on the right and a client VI on the left. The idea is to pass an FPGA reference and the FIFO name "FpgaDataIn" and the test VI grabs the FIFO by name and writes to the FIFO.

One issue to overcome is my beginner skills: the passed FPGA reference needs to be compatible with the FPGA reference control - which defeats the purpose of supporting generic FPGA references. There must be a way to specifiy a control that accepts a generic FPGA reference (dynamic FPGA cast? (which I've never used)).

Putting that issue aside for a moment, even when I define a FPGA reference control with a signature compatible with the passed FPGA reference I still get the 61206 error. I noticed issues related to upper/lower case and tried everything lower case (I THINK - I'm not positive I did it completely - but it's tedious with the FPGA reference signatures).

I read how the Get Single Resource Session needs a constant reference with a single "FIFO" fifo and have that.

Any tips?

Thanks!

Steve

03-26-2015 07:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

After rewriting, recompiling, AND using all lower-case for FIFO resource name, it worked 😃