- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Open/Close FPGA reference turns digital outputs on&of

Solved!01-24-2017 01:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a cRIO 9024 controlelr on a 9114 chassis with digital output module NI 9401.

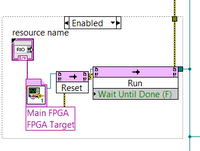

As shown in the first picture, when I use this code in the host VI for some reason all the digital outputs on the NI9401 go to high and then quickly go low.

It's the same at the end of the code when I use the Close FPGA Vi Reference

Now if I change it to the second picture, there's no low-to high- to low when I begin running the Host VI. But still the same problem when closing the FPGA reference

I'm wondering if I can stop this from hapenning.

Cheers

Solved! Go to Solution.

01-25-2017 12:50 AM - edited 01-25-2017 12:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello ErnestoB,

sorry for this

Why Does the Output of My NI 9401 Sometimes Glitch?

NI 9401 fpga reset method output glitch high

To workaround this issue, configure all channels on the module to be digital inputs and after the start programmatically to the needed outputs.

Alexander

01-25-2017 12:58 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can also partially work around this by disabling the "Reset" in close. If you right click on the Close FPGA Reference node you'll notice you can select between, "Close" and "Close and Reset if Last Reference". Note that this means that the FPGA VI will continue running after the session has closed and the host will more or less just be connecting to it without changing its state when you open a session again.

01-30-2017 10:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks everyone. I just decided it's easier to just unplug my digital output cables before turning on and off. I appreciate the responses!

06-04-2019 05:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Kudos to you M.S.!

I had no idea there were options on the close. This saves me from having to re-architect the code.

Thanks and Good Luck!

06-11-2019 07:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Michael_Strain wrote:

You can also partially work around this by disabling the "Reset" in close. If you right click on the Close FPGA Reference node you'll notice you can select between, "Close" and "Close and Reset if Last Reference". Note that this means that the FPGA VI will continue running after the session has closed and the host will more or less just be connecting to it without changing its state when you open a session again.

I did not know that. ![]()

06-11-2019 07:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

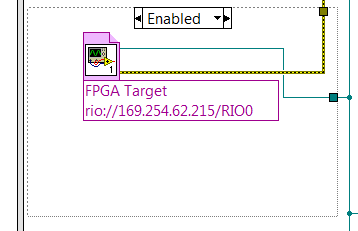

Regarding the OP post:

If you define the RIO reference in rio:// format, your DMA performance will be slower than if you simply name it "RIO0".

I found this out during benchmarking completely unrelated code.

Assuming of course the FPGA card is in the same chassis as the code accessing it, otherwise you'll need the IP address of course.

06-11-2019 09:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Intaris wrote:

Regarding the OP post:

If you define the RIO reference in rio:// format, your DMA performance will be slower than if you simply name it "RIO0".

I found this out during benchmarking completely unrelated code.

Assuming of course the FPGA card is in the same chassis as the code accessing it, otherwise you'll need the IP address of course.

Yes, if you use a resource string formatted like "rio://<host>/<device>" it opens a session over the network, even if the device is local to the system. This adds overhead going through the network stack. This link describes that more: Is There a Difference in How I Reference My FPGA Target?

In an upcoming release the Open node will begin setting a warning if you hit that specific case.