- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the most efficient way to replace array subset in this case on LabVIEW FPGA?

Solved!01-23-2019 10:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, this is a kind of quiz which asks the most efficient way to do the following thing on FPGA.

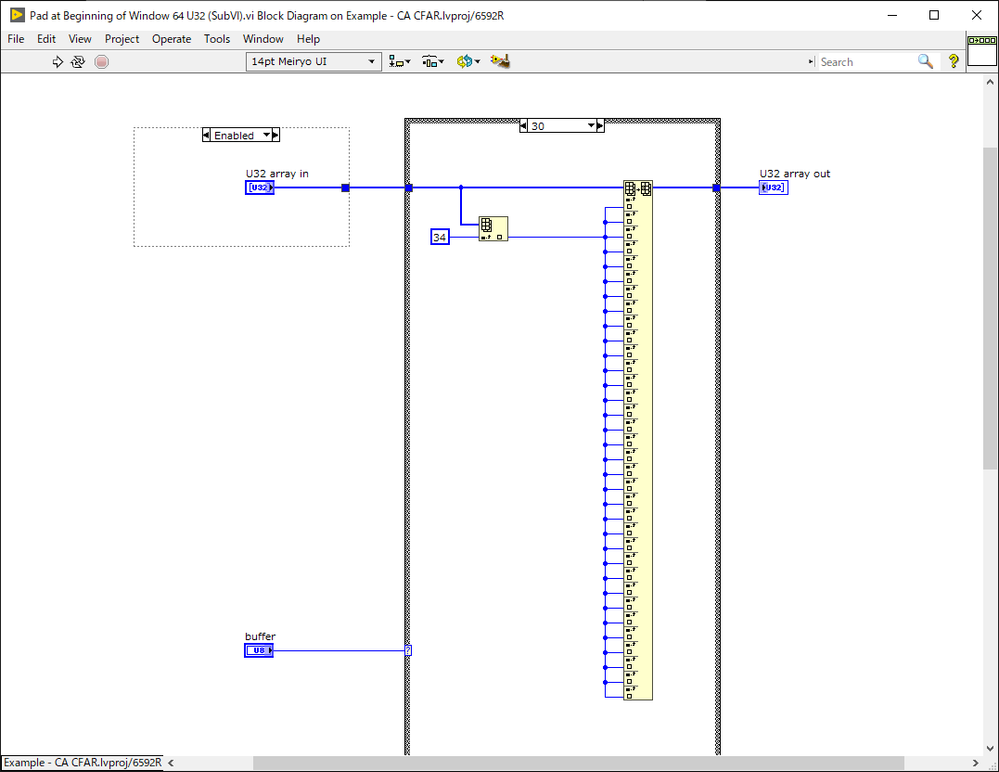

The VI attached on this post is the way I applied to what I would like to accomplish.

What I would like to accomplish is the following.

- There is an U32 array with 64 elements

- Specify an array index

- Replace all values before the index with the value specified by the array index.

Let's say, I have an array of [5, 6, 7, 8, 9]. If I specify 3 for array index, that points to 8 in that array. Then, the pointed value replaces all values before the index, so, resulted array is [8,8,8,8,9]. If I specify 1 for array index, 6 is pointed by the index, and the resulted array will be [6, 6, 7, 8, 9].

What is the most efficient way to accomplish this on LabVIEW FPGA? I tried various array functions such as Delete from Array, Replace Array Subset, Array Subset, etc, but Undefined Array Size error pops up at intermediate file generation.

If any smart people could share any idea, it would be really appreciated.

Thanks much in advance.

Solved! Go to Solution.

- Tags:

- fpga

01-23-2019 11:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

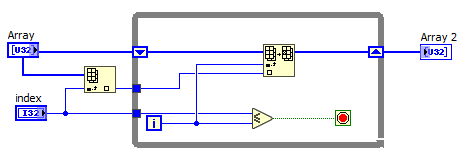

I would do something like this:

For added efficiency and speed, replace the while loop with a SCTL.

Regards, Jens

01-23-2019 01:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Auto-indexed for loop. If the index is less than or equal to the target index, use the new value; otherwise, use the existing value. You can even put this for loop inside a single-cycle timed loop (although note that there was and perhaps still is a bug where Select doesn't work inside a for loop inside a single-cycle timed loop; if so, use a case structure instead, see https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z0000019OLtSAM&l=en-US).

It would be an interesting experiment to look at the relative FPGA resource use of doing this inside versus outside a single-cycle timed loop as the array size grows. For a large array, putting it inside a single-cycle loop will cause a lot of copies of the comparator (which isn't that big, and if you know the value will fit in a U8 then I would cast to that to save space) but will of course execute in a single cycle. For a small array I doubt there will be much difference between inside and outside an SCTL.

01-23-2019 06:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello JensG69,

thanks for taking time to provide the idea.

I apologize that I did not clearly describe the requirement. I need to do the process within one clock cycle of SCTL. So, I cannot use any iterations.

01-23-2019 06:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello nathand ,

thanks for taking time to provide the idea.

I apologize that I did not clearly describe the requirement. I need to do the process within one clock cycle of SCTL. So, I cannot use any iterations.

01-23-2019 06:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As I mentioned in my post, you can put the for loop inside a single cycle timed loop. All iterations will execute in parallel.

If that's not clear, I'll try to post an example later when I'm in front of a computer.

01-23-2019 11:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi nathand,

Thanks much for the advice. Please do not take any more time at this moment, as I will try your idea right today. I will get back once I find anything. Thanks!

01-23-2019 11:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'd just coded this snippet when I saw your reply so I might as well post it. I don't have the FPGA toolkit installed but this is the right idea, just with the wrong appearance for the timed loop.

01-24-2019 02:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello nathand,

Thanks much again for teaching me the trick!

I tested it and it worked! I will follow your method in my project and it was a great learning. Thanks a lot!

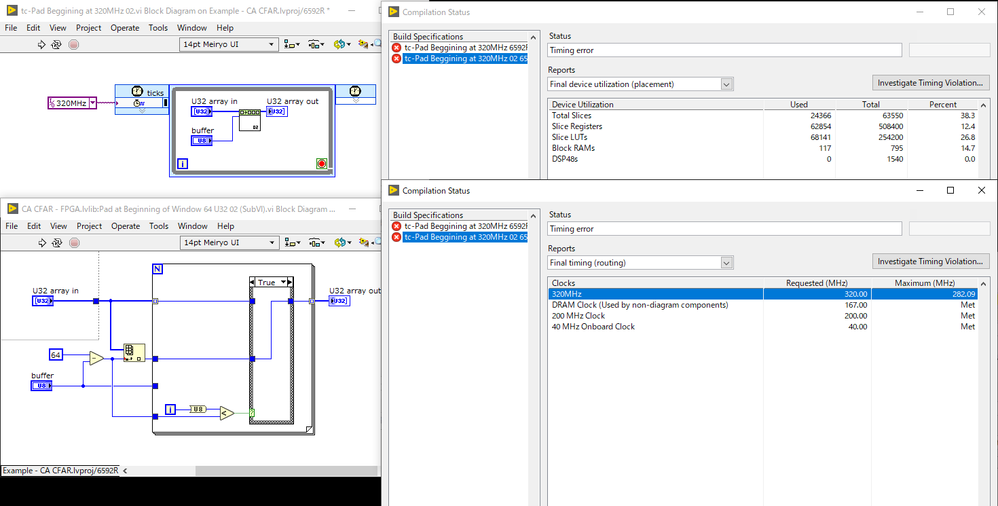

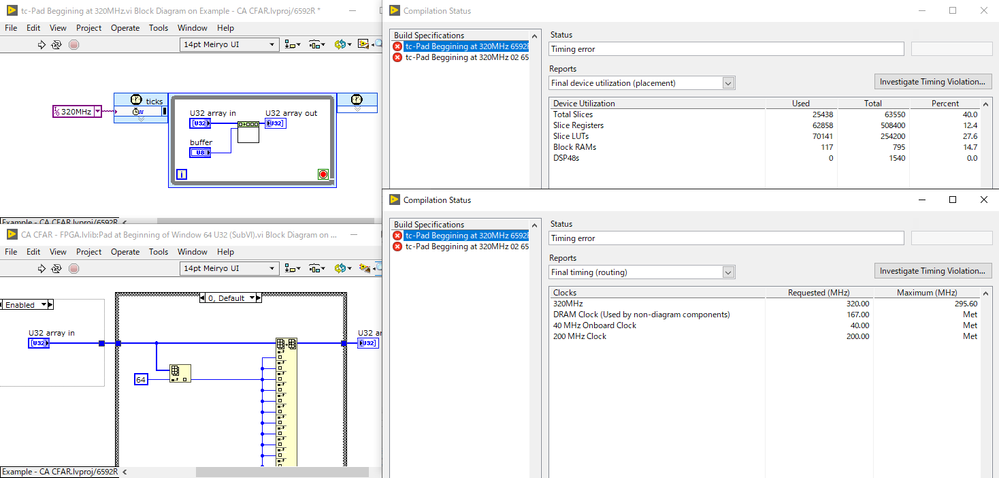

Just FYI, below is the result of my test.

Test conditions.

- LabVIEW 2017 SP1

- PXIe-6592R

- not removed implicit enable

- compiler setting == default

Below is your method and has many advantages compared to my original code.

- much much simpler than my original code.

- while Registers are used in almost the same amount, LUTs are saved about 2000 in Kintex7.

Below is my original code,

- its may reach up to 290MHz.