- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

how to use series modules and two different data rates in FPGA mode on cRIO 9075

Solved!06-21-2016 01:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

I have a project with modules namely NI 9227 (Modules 1) and NI 9234 (Modules 2)

The project is running and I am using TDMS write file and found that two channels are in the TDMS file while I am download the file using FTP from the cRIO.

1- My quesition is how to add a second data rate in the FPGA?

2- Why is TDMS is logging 4 channels and not 6 channels?

Thanks

Attached the projetc with two VIs

Solved! Go to Solution.

06-21-2016 04:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you looked at the getting started for the 9237 and been able to successfully acquire data for all of the channels on that device?

06-21-2016 04:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

I have a project with two modules namely NI 9227 (Modules 1) and NI 9234 (Modules 2)

The project is running and I am using TDMS write file and found that two channels are in the TDMS file while I am download the file using FTP from the cRIO.

1- My quesition is how to add a second data rate in the FPGA?

2- Why is TDMS is logging 4 channels and not 6 channels?

Thanks

Attached the projetc with two VIs

06-21-2016 04:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes

But I tried it alone on a separte VI.

Now I am looking to put as module 2 after the NI 9227 which is the main function of the project

06-22-2016 09:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Ihab,

I would try adding another while loop (in parallel with your current one) that writes Mod2's Analog Inputs to a separate FIFO. That way you'll be able to modify the 9234's sampling (data) rate via a separate I/O Property Node.

06-23-2016 01:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Alex,

Thank you for your reply.

This means that I cancel the Master Module (Data Rate) and Slave Module or keep this configuration as Master and slave data rate for modules?

Please confirm.

06-24-2016 09:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Ihab,

Sorry for the late reply here; just saw this message! If you'd like to keep the modules synchronized then definitely stick with the Master and Slave configuration for your two modules. Also note that you could sample slightly faster with the NI 9234 as your master module (since its internal master timebase is 13.1072 MHz instead of the 9227's 12.8 MHz timebase).

Please also see the Tips and Troubleshooting information in our guide for synchronizing C Series modules with LabVIEW FPGA:

http://zone.ni.com/reference/en-XX/help/373197D-01/target6devicehelp/sync_acq_multiple_modules/

Hope this helps!

06-28-2016 10:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

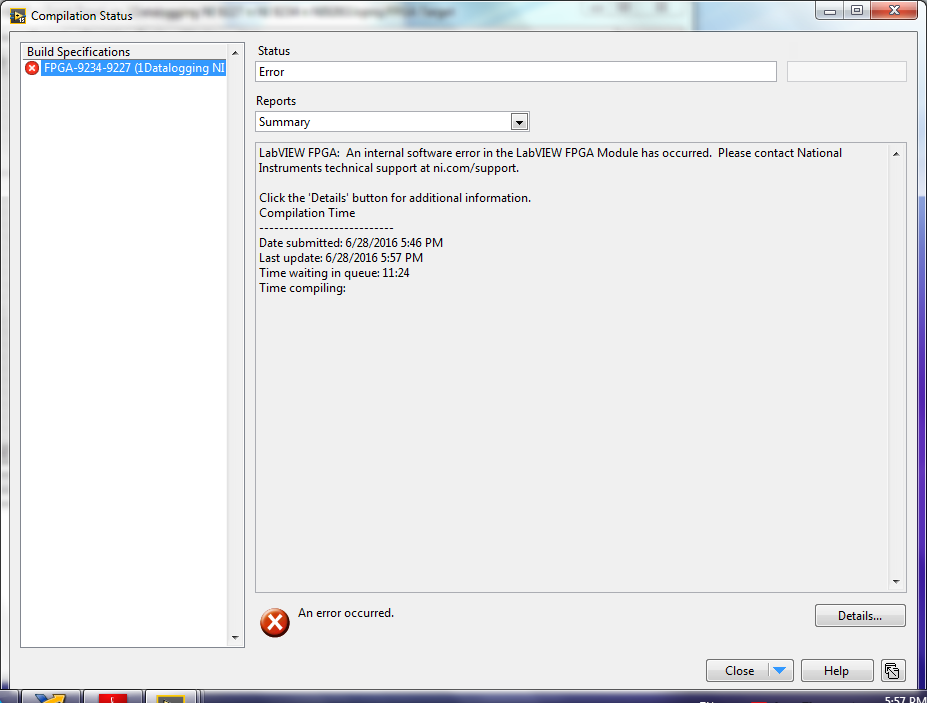

Hello Alex

I tried to apply the method you gave here.

I had error in compiling

attached the Project and FPGA vi