- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VeriStand FPGA XML Builder Node Feedback

07-11-2018 05:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

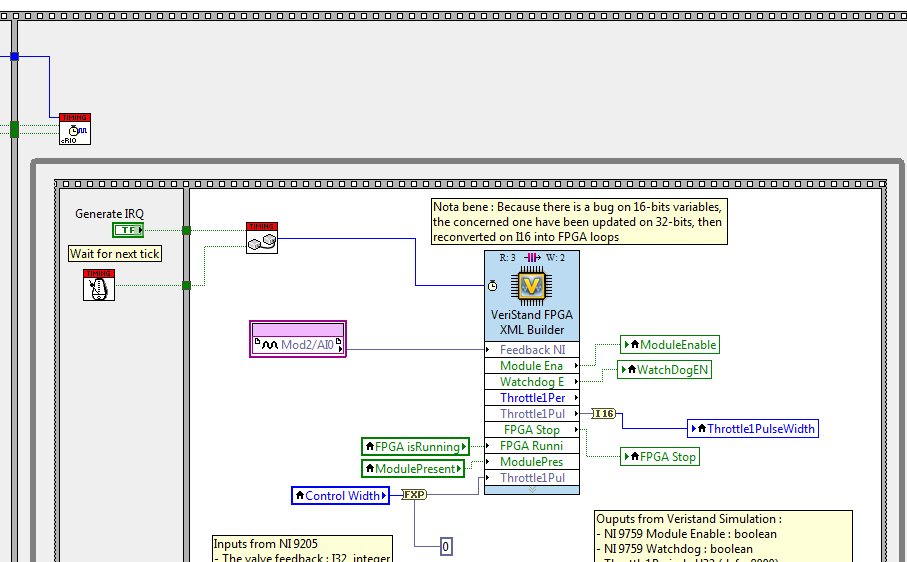

I don't know if this comes from Veristand 2017 or the XML Builder Node, but I couldn't transfer integer data (the FPGA never received anything)

Boolean transfer worked however.

the workaround was to use FXP for data transfer

Before (integer are not being transfered)

03-20-2019 08:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

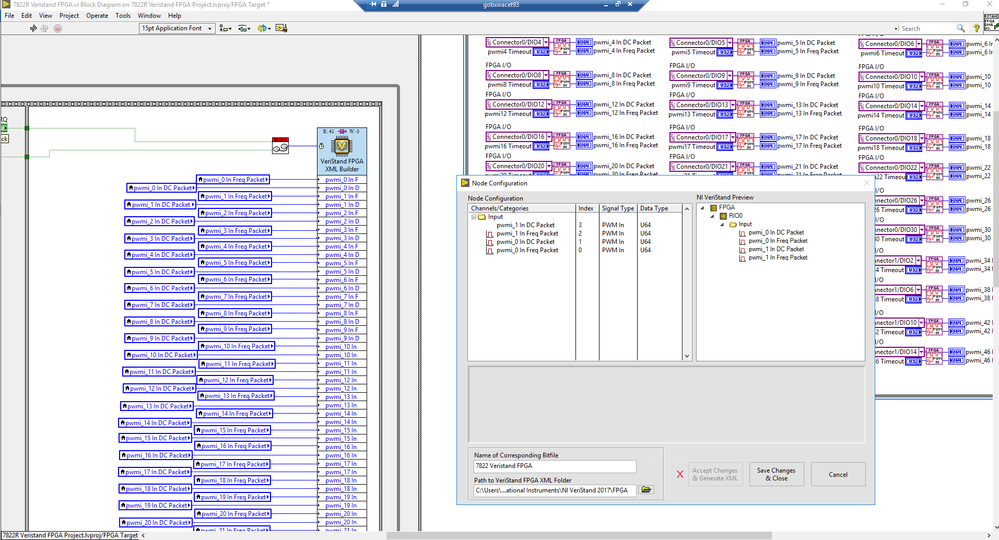

When I double click on the node I only see the first 4 signals that are mapped. All I am doing is measuring PWM Input frequency and Duty cycle which are 64 but unsigned numeric. Only the first 4 shows up and I get the error codes 1055 and 1136 as shown below. I have also attached a snapshot of the code. Any suggestions?

Date: 3/18/2019

Time: 2:16 PM

Error: 1055

Error Source: Property Node in Double Click Tree Read Tree subVI.vi->Node Configuration.vi->FPGA XML.xnode![]() nDoubleClick2.vi->FPGA XML.xnode

nDoubleClick2.vi->FPGA XML.xnode![]() nDoubleClick2.vi.ProxyCaller

nDoubleClick2.vi.ProxyCaller

Date: 3/18/2019

Time: 2:19 PM

Error: 1136

Error Source: Property Node (arg 1) in Double Click Build Tree SubVI.vi->Node Configuration.vi->FPGA XML.xnode![]() nDoubleClick2.vi->FPGA XML.xnode

nDoubleClick2.vi->FPGA XML.xnode![]() nDoubleClick2.vi.ProxyCaller

nDoubleClick2.vi.ProxyCaller

<APPEND>

Property Name: <b>Active Item:Tag</b>

Thanks

03-20-2019 05:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hmm, odd. Two quick thoughts:

1. I'd recommend a different approach. This node, and VeriStand's native FPGA implementation in general, is meant for data synchronization with the PCL. However, this doesn't matter for asynchronous operations like PWMs. You're better off looking at something like the FPGA Add-on custom device that accesses the bitfile directly vs using DMAs.

2. If you really want to use the node, I didn't look too closely at your code but it looks like you're treating them as PWM inputs instead of direct U64's. The PWM input types assumes the data is a joined representation of high and low (see documentation pdf on downloads page). I don't know if the node was stress tested for high counts of PWMs, but I've seen implementations with high integer counts so that should work.

03-21-2019 11:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ryan,

I have a problem:

I can generate the file .fpgaonfig and .lvbitx that are located in NI Veristand 2017>FPGA folder; the same folder where are the files NI VeriStand FPGA DMA.xsd and NI VeriStand FPGA DMA.xsl.

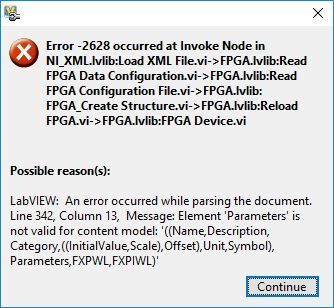

When I try to cofigure the FPGA using Veristand, the error appear.

What should I do?

03-27-2019 03:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Ryan,

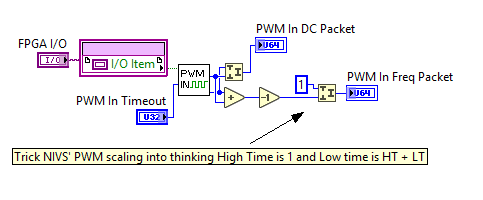

I tried using them as U64 as well but it still stops populating after 4 signals which is odd. The following shows what manipulation I am doing to get freq and dc packets. This is how our current project is implemented in NI 2013 versions but without the FPGA XML Builder, it was done using DMAs in the actual code. I tried to use the FPGA XML Builder Node to help create the fpgaconfig file automatically without having to manually create it. I have created a different project where I just use the NI RIO LIB for PWM available in the NI Veristand FPGA Support Palette which when wired to the PWM input of the FPGA XML Builder Node works fine, now I need to figure out what math i need to do in the system definition file to get the Freq and duty cycle value.

06-27-2019 07:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi.

Thank you for providing this tool. It makes my life a lot easier!

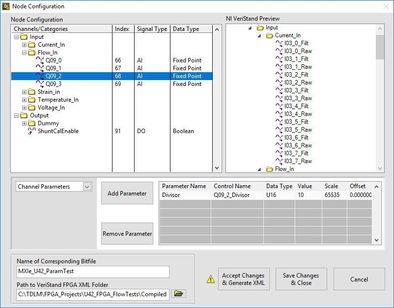

I have encountered an issue with the channel parameters option in the node.

If I add a parameter to a FXP input channel, all is well (no errors building xml) untill I try to load the fpgaconfig into Veristand.

I get error -2628

The XML looks like this:

<FXPI32> <Name>Q09_2</Name> <Description>VSE flowmeter (Quadrature encoder frequency)</Description> <Category>Input\Flow_In</Category> <InitialValue>0.000000</InitialValue> <Scale>1.000000</Scale> <Offset>0.000000</Offset> <Unit>Hz</Unit> <Symbol>AI</Symbol> <FXPWL>32</FXPWL> <FXPIWL>20</FXPIWL> <Parameters> <U16> <Name>Divisor</Name> <ControlName>Q09_2_Divisor</ControlName> <InitialValue>10</InitialValue> <Scale>65535.000000</Scale> <Offset>0.000000</Offset> </U16> </Parameters> </FXPI32>

After some experimenting, I found out that the issue is caused by the order of the tags in the XML. If I edit the XML manually and move the <FXPWL> & <FXPIWL> after the <Parameters> tag, Veristand accepts the configuration and shows the parameter in the system definition.

<FXPI32> <Name>Q09_2</Name> <Description>VSE flowmeter (Quadrature encoder frequency)</Description> <Category>Input\Flow_In</Category> <InitialValue>0.000000</InitialValue> <Scale>1.000000</Scale> <Offset>0.000000</Offset> <Unit>Hz</Unit> <Symbol>AI</Symbol> <Parameters> <U16> <Name>Divisor</Name> <ControlName>Q09_2_Divisor</ControlName> <InitialValue>10</InitialValue> <Scale>65535.000000</Scale> <Offset>0.000000</Offset> </U16> </Parameters> <FXPWL>32</FXPWL> <FXPIWL>20</FXPIWL> </FXPI32>

06-28-2019 01:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Pianne,

That's an interesting one. Unfortunately VeriStand is surprisingly rigid on the order of tags within the XML.

I don't think this node is receiving any upkeep (someone from NI can correct me if that's wrong), so your fastest workaround is likely to either continue to manually move the parameter XML or move your parameter to an integer channel (or create a dummy one if you don't have any).

Good luck! --Ryan_S

09-06-2019 09:41 AM - edited 09-06-2019 09:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I'm having some problems with this add-on. When I put the FPGA XML.vi on the block diagram labview starts to search NationalInstruments.Veristand.SystemStorageUI.dll and if I select Ignore all (as in other forum NI suggest us) the VI is grayed and I'm not able to go on.

I'm working on VS 2017

Thank you,

Fabio

I WAS WRONG IN THE INSTALLATION STEPS. sorry

09-06-2019 09:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Fabio,

Try looking for it in the Veristand program folder, eg:

C:\Program Files (x86)\National Instruments\VeriStand 2017\nivs.lib\Reference Assemblies\

09-06-2019 09:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Pianne,

I made an error in the installation. I didn't copy the config file before to run the vip.

Now it is ok,

thank you,

Fabio