- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Multi Channel RMS Calculations

02-27-2014 06:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I'm working with a cRIO-9112, which is doing some measurement and control. One of the problems I'm facing is that I don't have enough DSP48s. I would like to measure RMS values for three phases within the FPGA code, but it uses too many DSP48s to use three of the FPGA RMS blocks. My question is if there is a way to make it multi-channel, or even if there is a way to take accurate rms readings on the Real time side? Has anyone tried this?

Thanks

02-28-2014 07:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

DOjala,

Yes, it is certainly possible to implement a multichannel RMS. I have done this with good results. Thanks to BMac at NI for input and examples. I calculate the sum of squares in the FPGA VI and offload the averaging and square root operation to the RT VI.

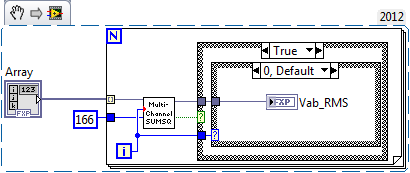

The array has the signals that I want to RMS. This resides in a while loop with 100us update rate and so the 166 samples implies 60Hz RMS calculation.

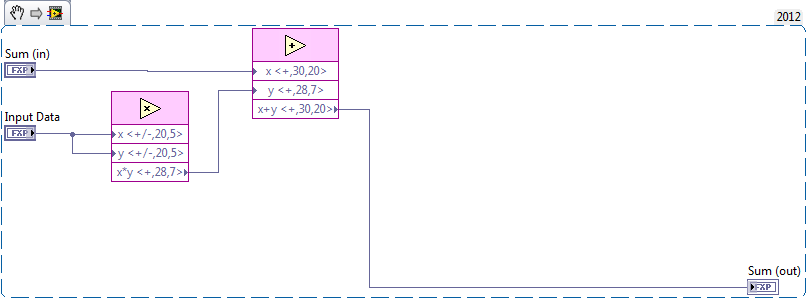

I am not sure how to attach VI's here but this is how the insides of the Multi-channel SUMSQ looks like:

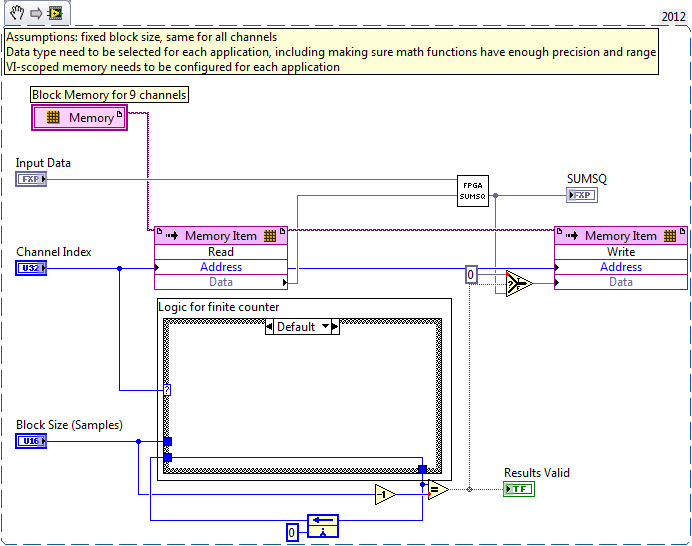

And this is how the FPGA SUMSQ looks like. NOTE: this VI is set to non-reentrant clone execution to save on DSP48's

02-28-2014 08:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Very nice! Please do attach your code.

Here's how to add an attachment in the discussion forums:

1. Click Use advanced editor in the upper right corner of the reply dialogue.

2. Click the Browse... button at the bottom left corner of the dialogue to attach the file(s).

02-28-2014 08:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here you go my friend.

The VI defined block memory is set to 9 channels because I needed 9. Modify as needed.

Cheers.

02-28-2014 10:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you! This will solve the problem. I hadn't thought of separating the calculation into two parts carried out in FPGA and Real Time. Smart.