- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can I sample 9215 AI channels separately at times differing by just a few FPGA ticks?

Solved!09-06-2011 12:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Howdy--

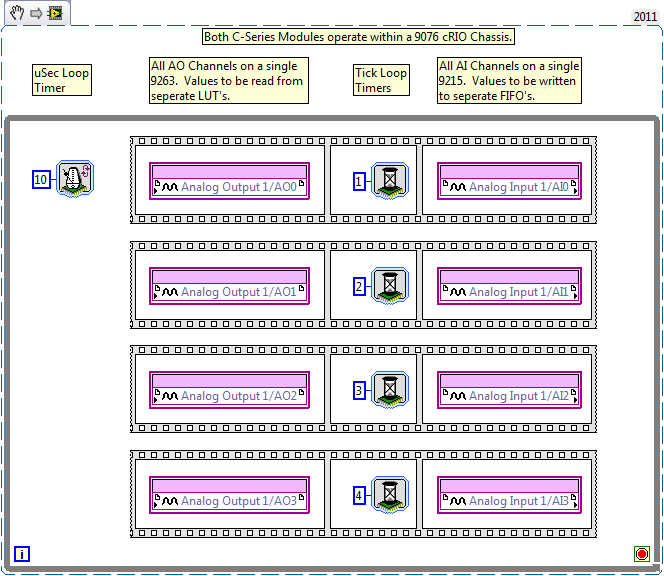

The image below is a crude illustration of my question. I would like to individually account for the delay between the excitation and response of 4 separated systems, each one connected to a single channel of a 9263 (excitation) and a 9215 (response). The minimum update delay on both modules is around 10 uSec, so I believe this would work if I simply wanted to read all the AI channels simultaneously. However, I haven't yet understood the 9215's inner workings enough know if I can sample the individual channels at times separated by a few FPGA clock ticks.

Thanks everyone, and have a great day.

Solved! Go to Solution.

09-07-2011 05:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi bcro,

With the 9215, all of the separate channels have separate ADCs, but still operate from the same 100kHz (10usec) clock as the module is limited to that sample rate.

So, in your case (thanks for the picture, by the way- that's always helpful!), what will happen is that all four of these Input channels from the 9215 will take place on the next loop cycle instead of staggered within the one iteration of the loop.

For instance, if you were to use a 40usec (25 kHz) loop rate, you could offset these delays at 10usec intervals and make this setup work, just not as quickly as you'd like.

Hopefully that explanation makes sense, but the short answer is that we won't be able to do that while running the loop at the minimum cycle time.

Austin S.

National Instruments

Academic Field Engineer

09-08-2011 09:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you, Austin, for your reply, and for answering my question better than I was able to ask it. The role of the module's 100 kHz clock was the real underlying issue I think I needed to understand there.