- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA master to FPGA 9144 communication?

11-18-2012 06:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

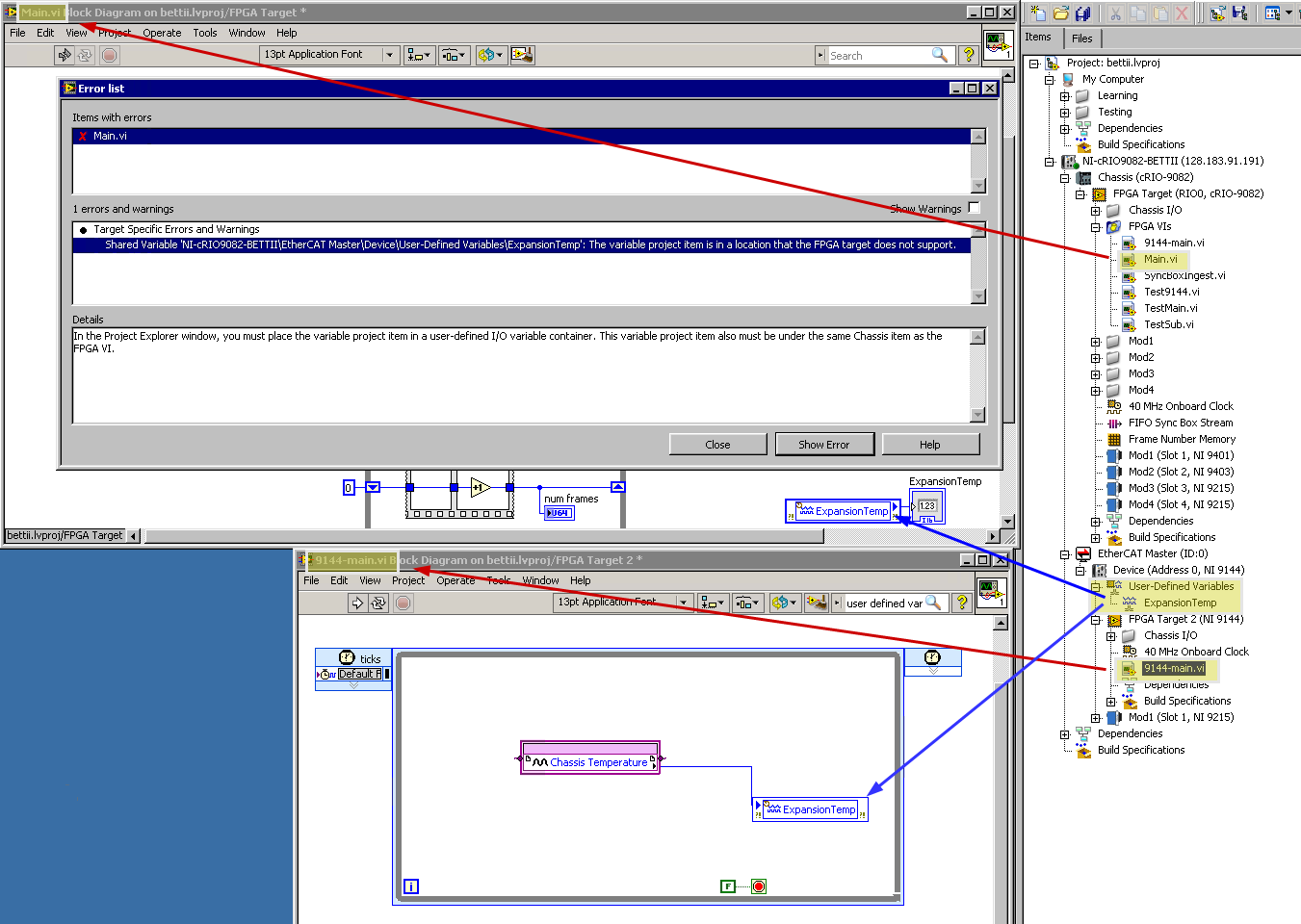

We want to run FPGA code on our NI 9144. How do I transfer data between FPGA code on the 9144 and FPGA code running on the master controller? The whitepaper Programming EtherCAT I/O With FPGA Intelligence describes using User Defined Variables to communicate with the NI 9144, but that is apparently only supported for communication with an RT program on the master controller. Belows is what happens when I try using the UDV in an FPGA program on the master contoller.

Steve

11-19-2012 12:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi maherhome,

In this case the Ethercat communication is handled by the RT Target, so in order to be able to pass some data from one FPGA to another FPGA from a different chassis you need to do it through the RT, the RT will receive the data and if you program it, you can have that data sent to the FPGA of your other device.

Regards,

AE | NI

11-19-2012 01:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That news was a bit shocking at first, but I'm getting used to it.

I guess if my timing requirements are more stringent than what channeling all communications through RT will allow, then I can setup a custom SPI network between the main and chasis using DIO modules and talk using FPGA.

Steve