- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Pop quiz! Test your understanding of channels!

06-17-2015 03:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

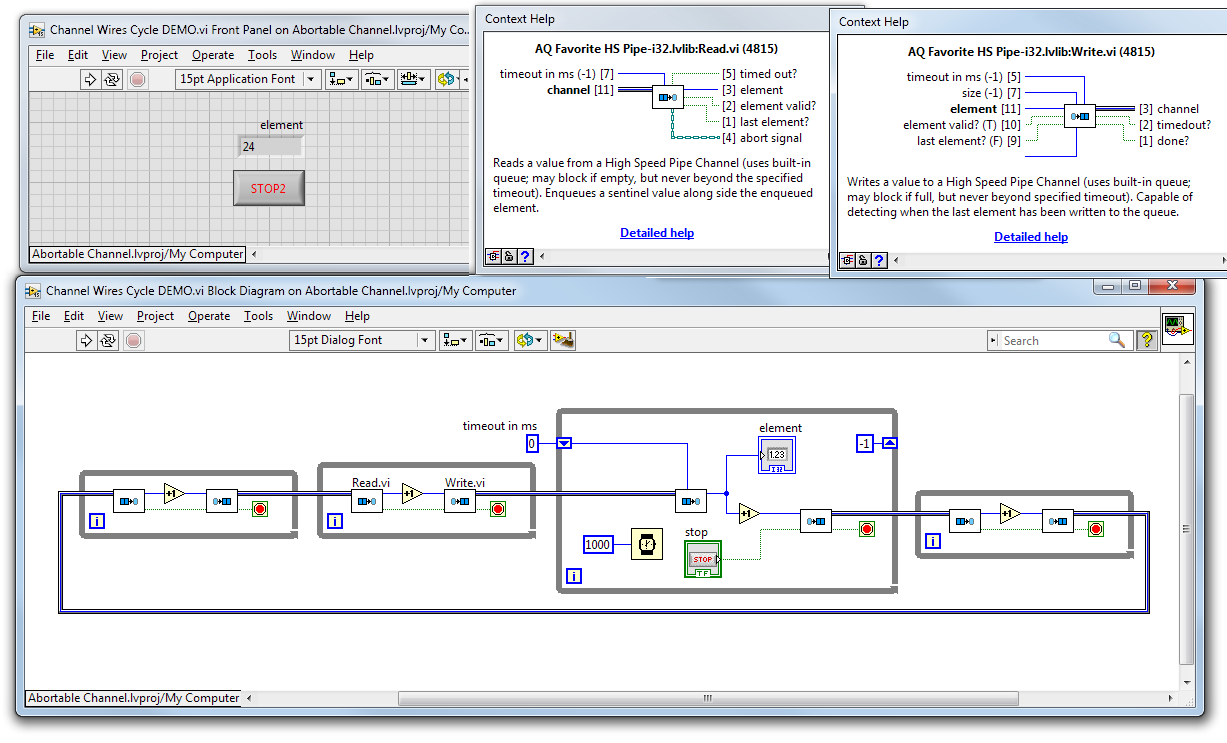

This is a screenshot of an interesting VI to contemplate. Test your knowledge of channels by answering the questions below.

1. Which loop begins first?

a) the left most

b) the second from left

c) the third from left

d) the right most

e) all of them try to run simultaneously

f) one of them begins first but exactly which one is a compiler decision

2. What are the values of "element" each time the third loop executes?

a) It displays increments of four, but it may display the same value several iterations in a row.

b) It displays increments of one, a different one each iteration.

c) It never displays anything because this VI hangs when you run it with all the loops waiting on each other.

d) It displays increments of four, a different one each iteration.

e) It displays increments of one most times but every once in a while the value increments by four in one iteration.

f) It displays the number 0 every iteration.

3. If you deleted the Wait Ms function from the third loop, what are the values of "element" each time the third loop executes?

a) It displays increments of four, but it may display the same value several iterations in a row.

b) It displays increments of one, a different one each iteration.

c) It never displays anything because this VI hangs when you run it with all the loops waiting on each other.

d) It displays increments of four, a different one each iteration.

e) It displays increments of one most times but every once in a while the value increments by four in one iteration.

f) It displays the number 0 every iteration.

4. What happens when the Stop button is pressed?

a) Nothing because the VI is hung with all loops waiting on each other.

b) The third loop from the left stops and the others keep running.

c) The third loop from the left stops and then the others stop in sequence so the VI halts.

d) The right most loop stops and then the others stop in sequence so that the VI halts.

e) The loops stop iterating but the VI doesn't halt because the loops are waiting on each other to complete.

f) The VI restarts as if the user had hit Abort and then hit the Run button again.

5. Suppose you did the following edits...

-- Replace (using the menu item) each of the current queue-based channel endpoints with the matching Tag channel endpoint that ships with LV 2015.

-- Remove all the broken wires on the diagram.

-- Wire the Stop button to the Stop terminal of the third loop.

-- Create a constant FALSE on the stop terminals of the other three loops.

(If you don't want to try to visualize this, check out the attached "EditToUseTags.png".)

When you run the VI, what are the values of "element" each time the third loop executes?

a) It displays increments of four, but it may display the same value several iterations in a row.

b) It displays increments of one, a different one each iteration.

c) It never displays anything because this VI hangs when you run it with all the loops waiting on each other.

d) It displays increments of four, a different one each iteration.

e) It displays increments of one most times but every once in a while the value increments by four in one iteration.

f) It displays the number 0 every iteration.

Answers are here, written in white text on a white background. Select the text to be able to see it.

Comments are moderated so no one just posts the answers!

Answer 1: E. All try to begin at the same time. Channel wires do not create a dataflow dependency between the loops, so this is no different than four parallel while loops on a diagram.

Answer 2: D. First value is zero. The zero is passed through the queues around the circle, getting incremented each time. When it comes back around, it is now 4. Repeat.

Answer 3: D. No change in behavior. The same thing happens but faster.

Answer 4: C. The stop signal is propagated through this particular channel wire.

Answer 5: C. This VI hangs because the Tag's Read endpoint blocks until the tag has been written to at least once and it does not have a timeout.

08-13-2015 10:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Really helpful Aristos, thanks for taking the time to put this together. I managed to get these right, but I think there was an element of expectation towards your example purpose rather than definitely knowing the correct answers ![]()

I'm interested in seeing examples that use these constructs across independent components/actors, to pass messages etc., something more than simple VIs. Without access to 2015 I'm unable to experiment with these, are there any on-line white-papers that cover larger use cases yet?

08-13-2015 04:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Everything that is online is on this community forum. What you see is all there is.

08-15-2015 08:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Giving a shot at the quiz...

<spoiler>

1) E-ish -- "one of them begins first but exactly which one is a compiler run-time/kernel scheduler decision"

2) Real answer should be A, but the "Wait 1000" combined with "My Computer" context in screenshot and assumption about OS and hardware based on today's date, in practice it's going to be D (strikeout moments after completing 3rd Q) It's D for sure. Shifting a -1 to timeout changes things; previous striked-out answer would be if the third loop kept the 0 timeout for subsequent iterations. One observation on the API: is it's hard know what the actual start value is since "Read" does not supply a "Default Value" (or perhaps, that's what the unlabeled wire is on the bottom of CH in Write?). I guess it's the (arbitrary) default value we know of that type to be 0

3) (just now reading this, LOL, based on just typing previous answer) Still A or D, but now more likely A Nope, D for sure, just a lot faster.

4) C is for "clean shutdown"

5) C, since "Blocks until the tag has been written to at least once" in CH. This API is way less useful, and I would probably never use it, and refactor any inherited code that did, because the likelihood of its design missing the most desirable semantics required for the application domain is probably high. (Note: based on CH, it's unclear if Read blocks only until the *first* existence of a message in its recv() buffer, or if it also blocks for subsequent iterations. If the former, this VI is chaos)

</spoiler>

As a post-mortem of taking this quiz, this block diagram streched my mind more than any diagram in a long time. Async wires fundamentally change the way you can see problems.

Even the way I ended up taking this quiz would have best been modeled with async wires. i.e., "start with what you know; compute; come back later and revise if things change elsewhere"

Thank you for creating this quiz, AQ! It was helpful (also acknowledging @Thoric's suspicion this is leading in a direction; it seems that's a good direction)

08-15-2015 08:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thoric wrote:

I'm interested in seeing examples that use these constructs across independent components/actors, to pass messages etc., something more than simple VIs. Without access to 2015 I'm unable to experiment with these, are there any on-line white-papers that cover larger use cases yet?

Having thought about this a lot since first seeing Async Wires...

I think that the value proposition of Async Wires is changing how we write procedural code at the functional level, not necessarily to replace all the endpoint configuration semantics needed at the systems/application-layer.

It could be argued a few ways... but I think the way to draw the line is this -- keep Async wires as deterministic as lossless as a CPU clock will allow, while having one other very similar type that's more tuned for messaging at a different layer.

08-17-2015 02:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

JackDunaway wrote:

Thoric wrote:

I'm interested in seeing examples that use these constructs across independent components/actors, to pass messages etc., something more than simple VIs. Without access to 2015 I'm unable to experiment with these, are there any on-line white-papers that cover larger use cases yet?

Having thought about this a lot since first seeing Async Wires...

I think that the value proposition of Async Wires is changing how we write procedural code at the functional level, not necessarily to replace all the endpoint configuration semantics needed at the systems/application-layer.

It could be argued a few ways... but I think the way to draw the line is this -- keep Async wires as deterministic as lossless as a CPU clock will allow, while having one other very similar type that's more tuned for messaging at a different layer.

Async wires are an unwelcome feature to my head. I'm very excited about their introduction, but they contradict years of brain training adapting to interpreting dataflow imagery. Suddenly cycles are permitted! The conflict is difficult to accede.

My mind is expanding to understand the full impact of Channels. In the short term my myopic vision sees them replacing existing functions to duplicate existing functionality more elegantly (messages across components), but their impact procedurally re-writes the rulebook somewhat, introducing theoretical chapters I've not yet discovered. Dang I wish I had LV2015 to actually play with these!

08-17-2015 11:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thoric wrote:

Async wires are an unwelcome feature to my head. I'm very excited about their introduction, but they contradict years of brain training adapting to interpreting dataflow imagery. Suddenly cycles are permitted! The conflict is difficult to accede.

My mind is expanding to understand the full impact of Channels. In the short term my myopic vision sees them replacing existing functions to duplicate existing functionality more elegantly (messages across components), but their impact procedurally re-writes the rulebook somewhat, introducing theoretical chapters I've not yet discovered. Dang I wish I had LV2015 to actually play with these!

This is exactly why we want the community, especially the skeptics, to give Channels a try. They do introduce a new layer of complexity, but so do things like referenc types in a dataflow world. The hope is that Channel wires make the communication layer simpler by providing a way to replace references that mask the actual communicators with something more explicit. All of you can help us figure out if that's actually the case or not. Hopefully you'll be able to get 2015 installed soon!

08-17-2015 02:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thoric wrote:

Suddenly cycles are permitted! The conflict is difficult to accede.

a) How do you feel about Feedback nodes?

b) Is there anything visually that we can do to draw the connection such that it shows a connection without implying "wire"? The current draw style came about after multiple people said, "you know, that channel doesn't really look like a regular wire; I think I could learn to 'see' it differently." But we may need to go further.

08-17-2015 03:48 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

AristosQueue wrote:

The current draw style came about after multiple people said, "you know, that channel doesn't really look like a regular wire; I think I could learn to 'see' it differently." But we may need to go further.

They still look like wires to me, and that's my biggest aversion to them. Maybe it's because I do so much object oriented work such that I don't really have an expectation of what a wire looks like.

I really don't like seeing those loops graphically connected. Having to explain data flow to a new user while hand-waving any time these constructs are used would be pretty awkward I imagine.

For starters I think the lack of a tunnel when crossing a loop boundary is way too subtle. Something obvious has to be there saying "hey this isn't data flow and I'm not a wire tunneling, indexing, or feeding back through this boundary". Something that doesn't exist anywhere else in LabVIEW.

For the record I *love* feedback nodes. Don't be messin' with them!

08-18-2015 01:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

AristosQueue wrote:

b) Is there anything visually that we can do to draw the connection such that it shows a connection without implying "wire"?

When I first saw these, I also had a similar problem. I tried playing around a bit with some other visual representations (semi-transparent wires (which possibly become opaque when hovering over them), "bridges" which look like they're going in front of the diagram, "underground tunnel entrances" which look like they're going behind the diagram, "mini bridges" which only skip over structure walls), but couldn't find something that looked good. I agree that some more effort should be put into this area.

___________________

Try to take over the world!