- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

veristand fpga scaling

03-02-2012 05:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello all,

I have a custom FPGA. In the FPGA, I pass a packet from the "Recieve Packet from Host.vi" into "Send Packet to Host.vi". At the VS workspace, I have a place to enter the values for the packet, and it also reads the values from the packet. In theory, anything I put in should come out exactly as it was. However, when I enter 700, I read back 1. When I enter -700, I read back -1. When I enter 0.3, I read back 0.3. Both sides of the .fpgaconfig looks like this (except I changed input with output):

<Packet>

<I16>

<Name>Test1</Name>

<Description>Analog input channel AI0 on connector 0.</Description>

<Category>Input\Analog</Category>

<Scale>1</Scale>

<Offset>0</Offset>

<Unit>NA</Unit>

<Symbol>AI</Symbol>

</I16>

<I16>

<Name>Test2</Name>

<Description>Analog input channel AI1 on connector 0.</Description>

<Category>Input\Analog</Category>

<Scale>1</Scale>

<Offset>0</Offset>

<Unit>NA</Unit>

<Symbol>AI</Symbol>

</I16>

<I16>

<Name>Test3</Name>

<Description>Analog input channel AI2 on connector 0.</Description>

<Category>Input\Analog</Category>

<Scale>1</Scale>

<Offset>0</Offset>

<Unit>NA</Unit>

<Symbol>AI</Symbol>

</I16>

<I16>

<Name>Test4</Name>

<Description>Analog input channel AI3 on connector 0.</Description>

<Category>Input\Analog</Category>

<Scale>1</Scale>

<Offset>0</Offset>

<Unit>NA</Unit>

<Symbol>AI</Symbol>

</I16>

</Packet>

03-05-2012 01:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi oeua.uoeuoau,

What version of NI VeriStand are you using?

What is the data type that you have setup for the DMA FIFO? I could see this behavior happening if your data type does not support +/- 700.

I realize that your XML file indicates I16's, but this doesn't make sense with a value of 0.3.

Have a great day,

Chris

National Instruments

03-05-2012 01:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Interesting point.

The FIFO is U64

03-05-2012 02:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The Scale and Offset defined in the XML are used to convert between the engineering units in NI VeriStand and the raw bits on the FPGA. In the case of fixed-point data types on the FPGA, this scaling is applied as you might expect (multiply the FXP value by the scale and add the offset to get the correct value in NI VeriStand). However, with integer data types such as I16, it is a bit more complicated.

Have a look at the NIVS help for the document entitled "Creating a Custom FPGA Configuration File". At the bottotm of this document is a section called "Understanding Scale and Offset" which explain the equations used for converting values for the packets defined in your XML. For the I16 data typoe, the following equations are used:

FPGA to NIVS: VV = DFV x (scale / P) + offset

NIVS to FPGA: DFV = (VV - offset) x (P / scale)

where VV is the voltage value in NIVS, DFV is the DMA FIFO value, and P is the positive range of the data type.

So, in this case, the scale is actually saying "take the entire range of values in an I16 and interpret them as values between -scale and +scale". Since you have defined your scale as 1, you're limiting the numeric values for this data type between -1 and 1. To see this, let's take a look at how the equations work for the path from NIVS -> FPGA -> NIVS.

With a value of 0.3:

DFV = (0.3 - 0) * (32767 / 1)

DFV = 9830.1

The value of 9830 is then passed as an I16 to the FPGA. This value is then passed back to NIVS:

VV = 9830 * (1 / 32767) + 0

VV = 0.299996948

So a value of approximately 0.3 is read back in NI VeriStand.

With a value of -700:

DFV = (-700 - 0) * (32767 / 1)

DFV = -22936900

The value of -22936900 is too large to store in an I16 data type (range -32768 to 32767). So the value is coerced into range, and the value -32768 is passed as an I16 to the FPGA. This value is then passed back to NIVS:

VV = -32768 * (1 / 32767) + 0

VV = -1.00003

So a value of approximately -1 is read back in NI VeriStand.

If you want to be able to pass a value of 700 to the FPGA and back, you will need to have your scale as 700 or greater (ex. Scale = 1000 would work). However, in your xml, it looks like you are trying to read the analog inputs of an R Series card. In this case, the values returned by the card will be voltage values between -10V and +10V scalled across the full range of an I16 data type. So if you set your Scale as 10 in your XML, you will read back the correctly scaled voltage value in NI VeriStand.

I hope that helps!

Regards,

Devin

03-05-2012 04:07 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you so much. It now works perfectly!

10-04-2012 03:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

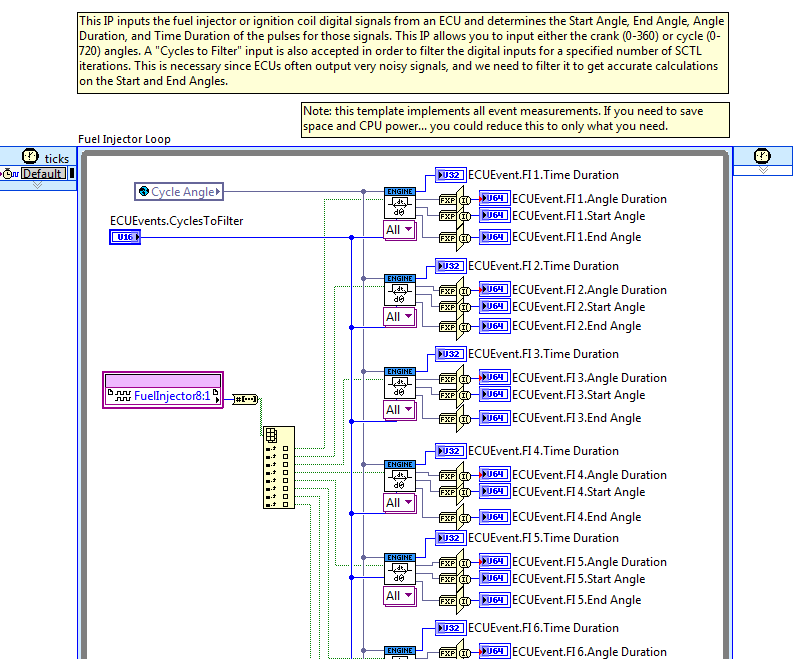

We are also facing similar problem regarding scaling. We are using AES library to generate Crank signal. We could generate the crank signal properly. In response to this we are getting injector pulses from ECU. For these pulses we are using AES ECU Event Measurement- Time Duration.vi to find out the injector ON duration. However the value observed in veristand is not matching with the time duration of actual injector signal. The time duration is in mili second. The Output of vi used, is in U64. We tried to use scaling formula available in help to calculate value of 'Scale'. But some how it is not getting matched.

Please guide us in this respect to resolve this issue.

10-04-2012 11:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you're using the AES library I don't recommend putting the event data back into the DMA FIFO. If you simply make indicators from the event measurement VI, the engine simulation custom device will read that data directly.

See the engine sim download and provided FPGA example.

10-20-2012 04:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Stephan,

Thanks for your reply.

We have our plant model in Matlab. We give measured injector fuel pulse width and angle value from custom device to plant model. Hence we need to give data to DMA FIFO. Hence only indicator option won't work. Scaling in fpga config file for these signals is a must.

Please guide us on this.

10-22-2012 09:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can provide the fuel pulse and angle value from the FPGA to the plant model without using the DMA FIFO. I don't recommend putting that data through the DMA FIFO. It will be much mroe work to set up the scaling, FPGA code, and system explorer if you put the data through the DMA FIFO.

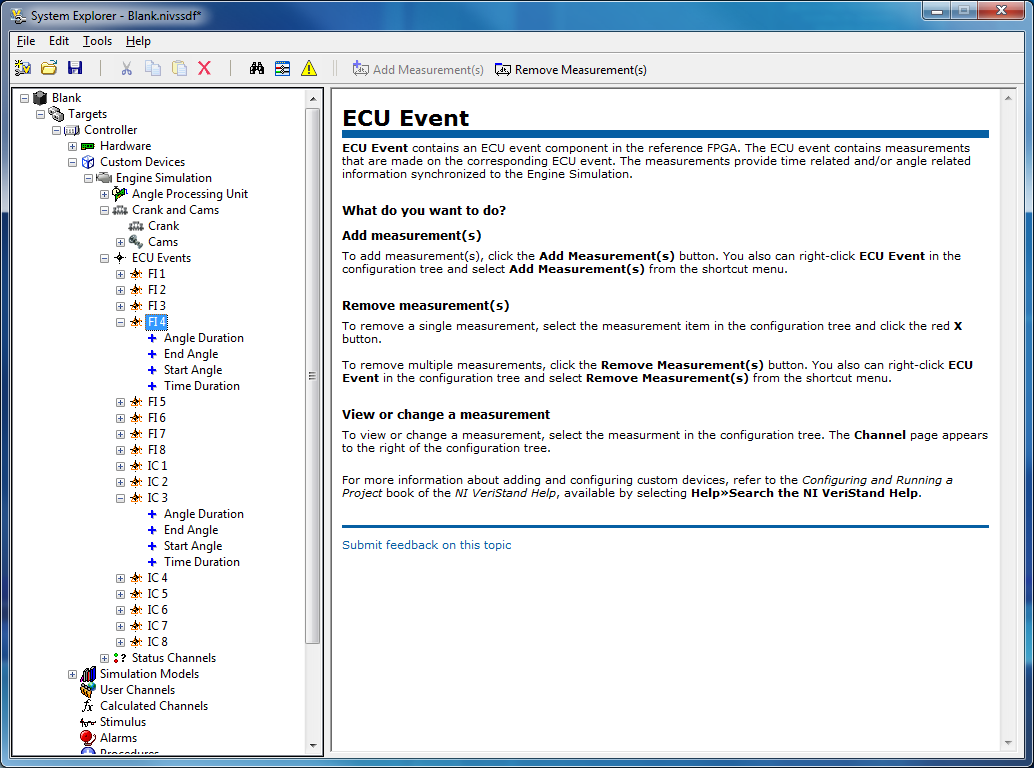

Instead, please use the Engine Simulation Custom Device with your bitfile. it was designed specifically to work well with the AES library. Read the link I provided. See if you name your event indicators according to the format (for example: "ECUEvent.<Component Name>.Angle Duration") then they will be automatically read by the custom device and scaled for you:

To see an example of this, the download for the custom device includes an FPGA project and VI: